英语原文共 13 页,剩余内容已隐藏,支付完成后下载完整资料

一种论述关于3D包装技术

选自——萨拉维、德里克雅培、保罗·弗兰松,他们都是电气与电子工程师学会会员。

摘要——这篇文章论述了最先进的3D包装技术整合在每一个大的领域。一些裸芯片和多芯片模块(MCM)堆叠技术正在出现,以满足不断增长的低功耗需求,重量轻,便携式系紧凑系统。垂直互联技术被详细的提及到。诸如硅效率,复杂性,热管理,互连密度,速度,功率等技术问题。取决于目标应用的3D堆叠技术方面的选取是很重要的,被反复提及到。

关键词 - 裸芯片堆叠,MCM堆叠,3D MCM技术,3D封装,垂直互连。

一、引言

随着便携式电子系统的复杂性增加,例如从移动电话向互动移动多媒体个人通信器(IM PC)的范式转变[1],对低功耗,低重量和小巧的生产提出了更高的要求 用于VLSI集成电路的封装技术。 同样,许多航空和军事应用都遵循这一趋势。 为了满足这一需求,现在出现了许多新的三维(3-D)封装技术,其中裸芯片或多芯片模块沿着这些技术堆叠,导致紧凑性有着显著的改善。 由于这种平面技术导致总体互连长度低得多,因此寄生电容和系统功耗可以降低多达30%[2]。

第二部分将讨论三维封装技术的优势及其对系统性能的影响。 第三节将简要讨论三维封装中使用的不同垂直相互连接方法,第四部分将讨论三维技术的局限性。

二、三维包装技术的优势

以下小节讨论了3-D打包技术如何提高系统性能,并提供使用常规封装技术无法实现的性能因素。

手稿1997年4月30日收到; 1997年8月20日修订。这项工作得到了澳大利亚国防科技组织(DSTO)的部分支持。

萨拉维和德里克雅培都是来自阿德莱德大学,电气与电子工程系,高性能集成技术与系统中心,位于南澳大利亚阿德莱德5005(电子信箱:alsarawi @ eleceng .adelaide.edu.au; dabbott@eleceng.adelaide.edu.au)。

保罗·弗兰松来自北卡罗来纳州立大学电气和计算机工程系,罗利,NC 27695 USA(电子邮件:paulf@eos.ncsu.edu)。

出版商物品识别号S 1070-9894(98)00595-7。

- 尺寸和重量

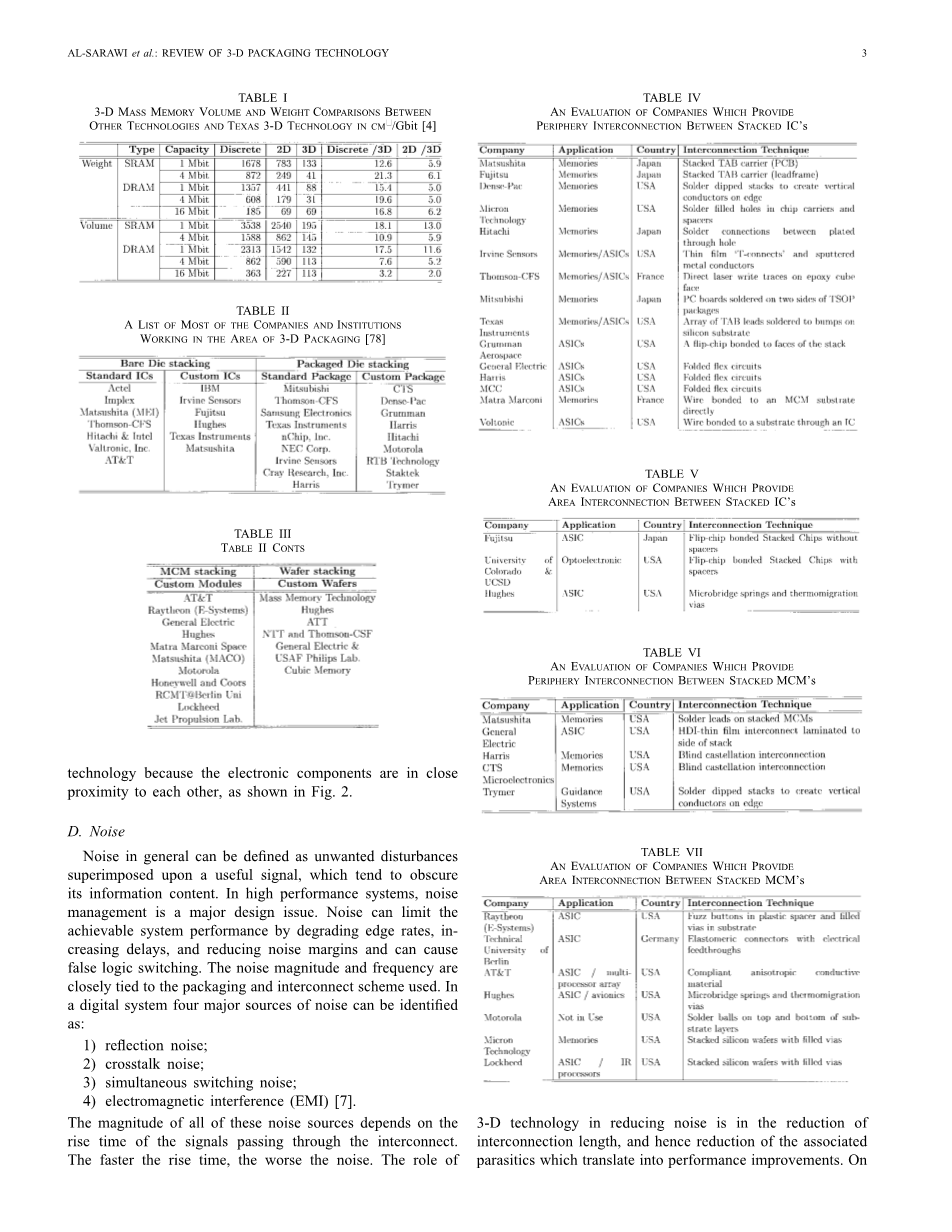

通过用3-D器件代替单芯片封装,实现了重量的大幅度减轻。这些削减的重要性在一定程度上取决于纵向互连密度和可访问性,这将在第II-G部分,热特性和所需的坚固性中得到讨论。据报道,与常规包装相比,使用3-D技术可以实现40至50倍的尺寸和重量的减小。作为一个例子,TI的3-D裸机封装和离散和平面封装(MCM)之间的体积和重量比较见表I-VII。从这些表中可以看出,MCM技术的体积减少了五到六倍,而离散的封装技术减少了10到20倍。此外,与MCM技术相比,重量减少了2至13倍,与分立组件相比,减少了3到19次。所有这些减少都是由于消除了与传统技术相关的头顶重量和尺寸。此外,在阿拉丁并行处理器[3]的情况下,与Cray X-MP基准相比,尺寸和体积的减少分别为约660和2700倍。

- 硅效率

封装技术的主要问题之一是芯片占用面积,这是芯片占用的印刷电路板面积[5],如图1所示。 1.在MCM案例中,由于使用裸芯片,占地面积减少了20-90%。 三维封装可以更有效地利用硅片,这被称为“硅效率”。我们可以将硅效率定义为堆叠中基板总面积与占用面积的比例。 因此,与其他二维(2-D)封装技术相比,3-D技术超过了100%的硅效率。

- 延迟

延迟是指信号在系统中的功能电路块之间行进所需的时间。 在高速系统中,总的延迟时间主要受到飞行时间的限制,这是随着信号沿互连行进所花费的时间而定义的[6]。 光纤的时间与互连长度成正比。 因此,减少延迟需要减少使用3-D封装时的互连长度,如图3所示。 由此导致的互连长度减小导致互连相关的寄生电容和电感的减小,因此降低信号传播延迟。 例如,作为使用MCM的结果的信号延迟减少约300%。此外,在3D技术的情况下,延迟应该会更小,因为3D技术电子元件彼此之间都靠的很近,如表2所示。

表1

其他技术与3D技术在三维质量记录仪中体积和重量之比[4]

|

类型 |

容量 |

离散性 |

2D |

3D |

离散性/3D |

2D/3D |

|

|

重量 |

静态存储器 |

1兆 |

1678 |

783 |

12.6 |

5.9 |

|

|

4兆 |

872 |

249 |

21.3 |

6.1 |

|||

|

动态存储器 |

1兆 |

1357 |

441 |

15.4 |

5.0 |

||

|

4兆 |

608 |

179 |

19.6 |

5.0 |

|||

|

16兆 |

185 |

69 |

16.8 |

6.2 |

|||

|

体积 |

静态存储器 |

1兆 |

3538 |

2540 |

18.1 |

13.0 |

|

|

4兆 |

1588 |

802 |

10.9 |

5.9 |

|||

|

动态存储器 |

1兆 |

2313 |

1542 |

17.5 |

11.6 |

||

|

4兆 |

862 |

500 |

7.6 |

5.2 |

|||

|

16兆 |

363 |

227 |

3.2 |

2.0 |

|||

表2

三维包装领域的大多数公司和机构清单[78]

|

裸芯片堆叠 |

包装模具堆叠 |

平面封装堆叠 |

胶封堆叠 |

||

|

杰出信息系统公司 |

普通信息系统公司 |

杰出包装 |

普通包装 |

普通模块 |

普通胶封 |

|

Actel Matsushita Thomson-CFS Hitachiamp;Intel Valtronic,Inc ATamp;T |

IBM Irvine Sensors Fujitsu Hhgbes Texas Instruments Matsushita |

Mitsubishi Thomson-CFS Samsung Electronies Texas Instruments nChip,Inc NEC Corp Irvinc Sensors Cray Research,Inc Harris |

CTS Dense-Pac Grumman Harris Hitachi Motorola RTB Technology Staktek Trymer |

ATamp;T Raytheon Genral Electric Hnghes Matra Marconi Space MACO Motorola Honcywell and Coors RCMT Berlin UM Lockhead Let Propulsion Lab |

Mass Memory Technology Hughes ATT NTT and Thomson-CFS Genral Electric amp; USAF Philips Lab Cubic Memory |

表4

在堆叠信息系统之间提供周边互连的公司的评估

|

公司 |

应用 |

国家 |

技术简介 |

|

Matsushita Fujitsu Dense-Pac Micron Technology Hitachi Irvine Sensors Thomson-CFS Mitsubishi Texas Instruments Grutoman Aerospace Genral Electric Hanis MCC Matra Marconi Voltonic |

记忆 记忆 记忆 记忆 记忆 记忆/信息系统 记忆/信息系统 记忆 记忆/信息系统 信息系统 信息系统 信息系统 信息系统 记忆 信息系统 |

日本 日本 美国 美国 日本 美国 法国 日本 美国 美国 美国 美国 美国 法国 美国 |

叠片载体 叠片载体 焊料浸堆上创建边缘垂直导体 焊料填充孔的芯片载体和间隔 焊料连接镀通孔 信息连接薄膜和溅射金属导体 环氧立方面直接激光写入痕迹 电路板焊接在两侧的小尺寸封装 在硅衬底上焊接到凸块的标签引线阵列 倒装芯片粘结到堆栈的面 折叠柔性电路 折叠柔性电路 折叠柔性电路 直接写入平面封装衬底 通过集成电路写入衬底 |

表5

对堆叠集成电路提供区域互连的公司的评价

|

公司 |

应用 |

国家 |

技术简介 |

|

Fujitsu University of Colorado amp; UCSD Hughes |

信息交换系统 光电 信息交换系统 |

日本lt; 剩余内容已隐藏,支付完成后下载完整资料 资料编号:[140603],资料为PDF文档或Word文档,PDF文档可免费转换为Word |

课题毕业论文、外文翻译、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。