英语原文共 3 页,剩余内容已隐藏,支付完成后下载完整资料

数字调制的FPGA实现

方案:使用VHDL的BPSK和QPSK

Rajib Das

欧洲经委会部,印度西孟加拉邦J. C. Bose爵士工程学院

摘要

本文介绍了数字调制的仿真结果 方案BPSK和QPSK。 数字调制不太复杂, 在长距离传输中更安全,更高效。该 数字噪声检测和校正比效率更高 模拟。 因此它在现代通信中更为重要 系统。 可以使用这些数字调制方案来实现 FPGA(现场可编程门阵列)。 在本文中,BPSK和 QPSK调制技术已在FPGA上实现 使用VHSIC(超高速集成电路)硬件 Xilinx ISE 14.1上的描述语言(VHDL)并进行了仿真 使用MdelSim SE 6.0

关键词

数字调制技术,BPSK,QPSK,FPGA,VHDL

简介

尽管BPSK具有简单的发射器和接收器架构 调制器,BPSK调制仍然普遍用于无线 WPAN(无线个人局域网)等通信 [1]。 QPSK用于不同的通信系统,如CDMA ,3G,Wi-Fi(IEEE 802.11)和WiMAX(IEEE 802.16)。该 QPSK所需的带宽是BPSK所需的带宽的一半 QPSK中的误码率(BER)和传输数据速率相同 因减速带宽而更高。 现场可编程门阵列(FPGA)是半导体 包含可编程逻辑元件(LE)和a的设备 可重构互连的层次结构,以实现任何复杂的 组合或顺序逻辑功能。今天的FPGA 由可配置的嵌入式静态随机存取存储器组成 (SRAM),高速收发器,高速输入/输出 (I / O)元素,网络接口,甚至硬嵌入 处理器。一项文献调查显示,FPGA被广泛使用 在不同的应用中,如电机控制器[2],神经元 网络实现[3-5],有限脉冲响应(FIR) 滤波器实现[6-7],模糊逻辑控制器[8]等.

BPDK调制器

在二进制相移键控(BPSK)中,正弦相位 载波信号根据二进制的值而变化 要发送的信息数据位。 它也被称为双相 调制或相位反转键控[9]。 载体的阶段 信号在二进制数据的0ordm;和180ordm;之间变化。该 BPSK信号可表示为:

其中,一个sin(2pi;ft)是0°初始相位的载波信号。当输入二进制数据从1变为0,反之亦然,即BPSK输出信号相位从0ordm;移位到180ordm;,反之亦然。

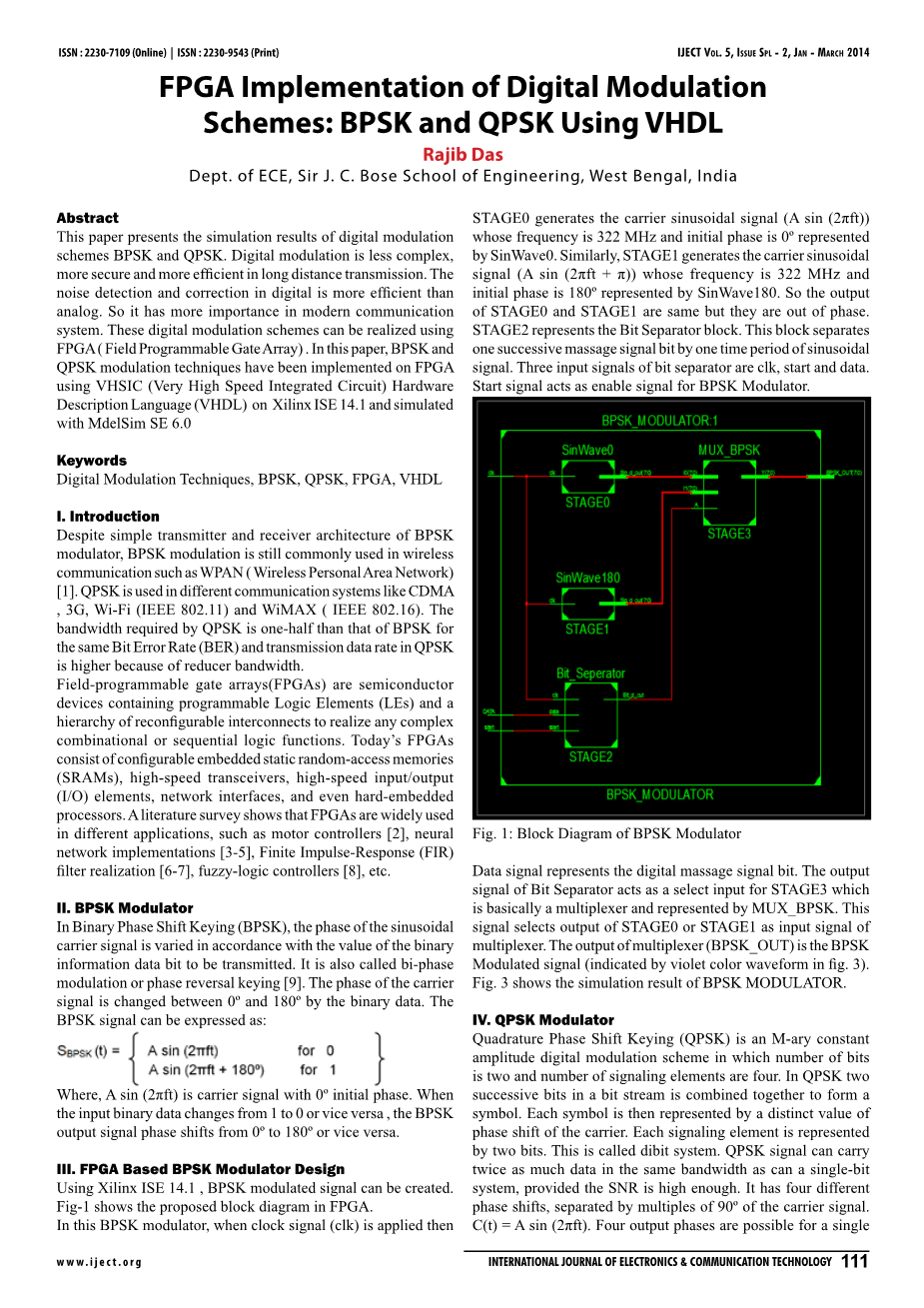

基于FPGA的BPSK调制器设计

使用Xilinx ISE 14.1,可以创建BPSK调制信号。图 1显示了FPGA中提出的框图。 在这个BPSK调制器中,当应用时钟信号(clk)时 STAGE0产生载波正弦信号(A sin(2pi;ft)) 其频率为322 MHz,初始相位为0° 由SinWave0撰写。类似地,STAGE1生成载波正弦波 信号(A sin(2pi;ft pi;)),其频率为322 MHz和 初始阶段是SinWave180代表的180ordm;。所以输出 STAGE0和STAGE1的相同但它们是异相的。 STAGE2表示位分隔符块。这个区块分开了 一个连续的按摩信号位一个正弦周期 信号。位分离器的三个输入信号是clk,start和data。 启动信号用作BPSK调制器的使能信号。

图 1:PSK调制器的框图

数据信号代表数字按摩信号位。输出 位分离器的信号用作STAGE3的选择输入 基本上是一个多路复用器,由MUX_BPSK表示。这个 信号选择STAGE0或STAGE1的输出作为输入信号 复用器。多路复用器(BPSK_OUT)的输出是BPSK 调制信号(图3中的紫色波形表示)。图 3显示了BPSK MODULATOR的模拟结果。

QPSK调制器

正交相移键控(QPSK)是M-ary常数 幅度数字调制方案,其中位数 是两个,信令元素的数量是四个。在QPSK两个 比特流中的连续比特被组合在一起以形成 符号。然后每个符号由不同的值表示 载波的相移。表示每个信令元素 两位。这被称为dibit系统。 QPSK信号可以携带 在相同带宽中的数据是单比特的两倍 系统,只要SNR足够高。它有四种不同 相移,由载波信号的90°的倍数分隔。 C(t)= A sin(2pi;ft)。单个可能有四个输出阶段 IJECT Vol。 5,发行Spl - 2,2014年1月至3月ISSN:2230-7109(在线)| ISSN:2230-9543(打印) 112国际电子通信技术期刊www.iject.org载波频率,对应于00,01,10和11个双位。每 dibit代码生成四个可能的输出阶段之一(0ordm;, 90ordm;,180ordm;,270ordm;)。每个输出阶段发生一次变化 两位多比特。输出的变化率(波特率)等于输入比特率的一半。 在数学上,QPSK信号持续一个符号, 每个由两位组成,可表示为:

表 1符号,位和符号之间的关系,PSK载波信号的相移[9]

表 1:QPSK信号中的符号位和相移

|

Symbol |

Bit in symbol |

Phase shift in carrier signal |

|

S1 |

0 0 |

0ordm; |

|

S2 |

0 1 |

90ordm; |

|

S3 |

1 0 |

180ordm; |

|

S4 |

1 1 |

270ordm; |

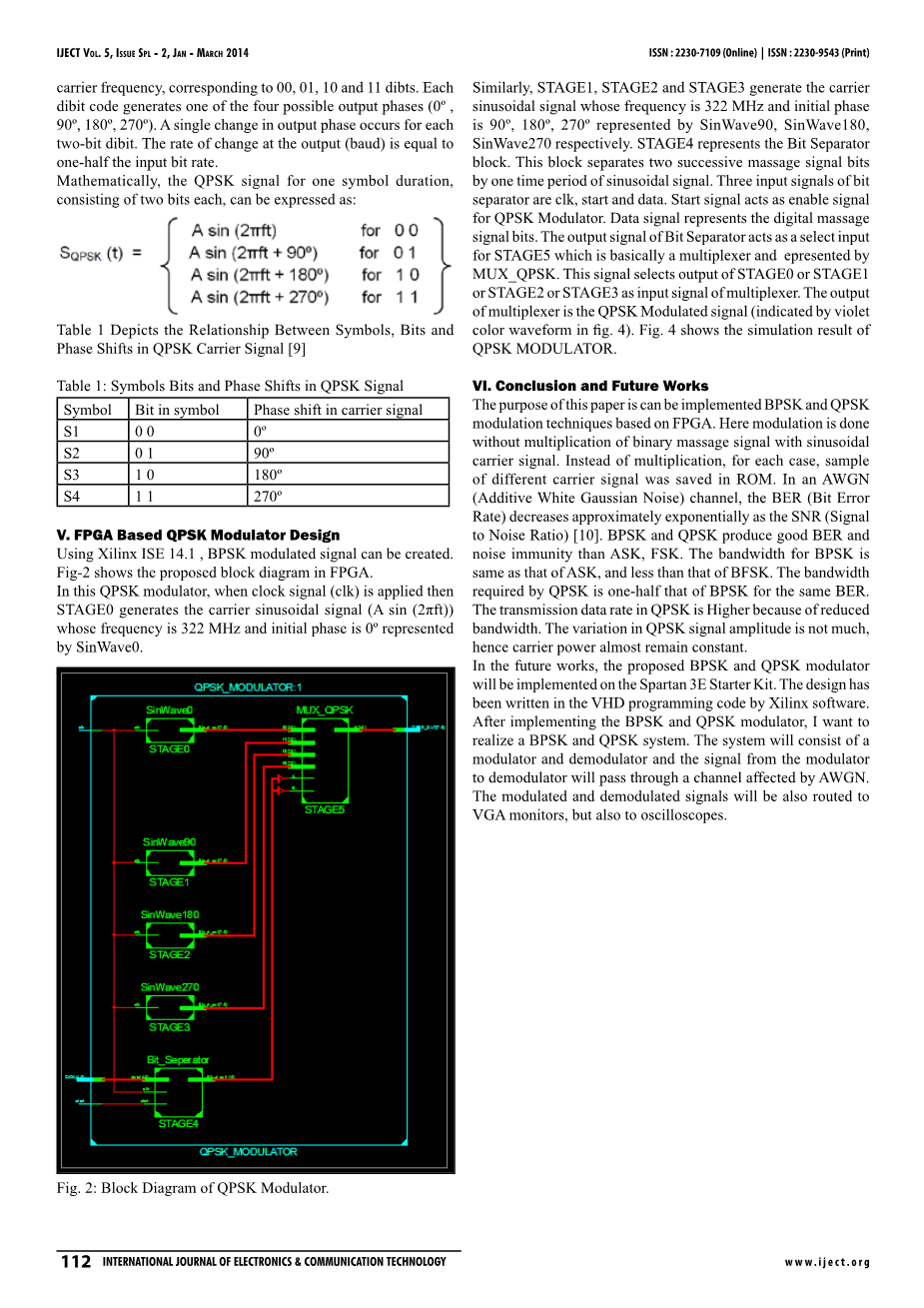

基于QPSK的FPGA调制器设计

使用Xilinx ISE 14.1,可以创建BPSK调制信号。图 2显示了FPGA中提出的框图。 在这个QPSK调制器中,当应用时钟信号(clk)时 STAGE0产生载波正弦信号(A sin(2pi;ft)) 其频率为322 MHz,初始相位为0° 由SinWave0撰写。

图 2:QPSK调制器的框图。

类似地,STAGE1,STAGE2和STAGE3生成载波 正弦信号,其频率为322 MHz,初始相位 由SinWave90,SinWave180代表的90ordm;,180ordm;,270ordm;, SinWave270分别。 STAGE4代表位分隔符 块。该块分隔两个连续的按摩信号位 一段时间的正弦信号。位的三个输入信号 分隔符是clk,start和data。启动信号用作启用信号 用于QPSK调制器。数据信号代表数字按摩 信号位。位分离器的输出信号用作选择输入 对于STAGE5来说,它基本上是一个多路复用器,由epresent提供 MUX_QPSK。该信号选择STAGE0或STAGE1的输出 或STAGE2或STAGE3作为多路复用器的输入信号。输出 多路复用器是QPSK调制信号(用图4中紫色波形表示)图 4显示了模拟结果 QPSK MODULATOR。

总结和未来的工作

本文的目的是实现BPSK和QPSK 基于FPGA的调制技术。这里完成了调制 没有二进制按摩信号与正弦的乘法 载波信号。对于每种情况,样本而不是乘法 不同的载波信号保存在ROM中。在AWGN中 (加性高斯白噪声)通道,BER(误码 速率)随着SNR(信号)大致呈指数下降 噪音比率)[10]。 BPSK和QPSK产生良好的BER和 噪声抗扰度比ASK,FSK。 BPSK的带宽是 与ASK相同,少于BFSK。带宽 对于相同的BER,QPSK所需的是BPSK的一半。 QPSK中的传输数据速率因降低而更高 带宽。 QPSK信号幅度的变化不大, 因此载波功率几乎保持不变。 在未来的工作中,提出了BPSK和QPSK调制器 将在Spartan 3E入门套件上实施。设计有 由Xilinx软件编写的VHD编程代码。 实现BPSK和QPSK调制器后,我想 实现BPSK和QPSK系统。该系统将包括一个 调制器和解调器以及来自调制器的信号 解调器将通过受AWGN影响的信道。 调制和解调的信号也将被路由到 VGA显示器,也适用于示波器。

引用

【1】H. C. Park,“功率和带宽有效的恒定包络 BPSK信号及其连续相位调制“,IEE Proceedings Communications,Vol。 2005年6月第152号,第152号.

【2】 B. Alecsa,A。Onea,“设计,验证和FPGA实现 无刷直流电机速度控制器“, 第17届IEEE国际会议论文集 电子,电路和系统(ICECS),12月12日 - 15,2010,pp.1112-1115.

【3】 S. Himavathi,D。Anitha,A。Muthuramalingam,“前馈 基于FPGA的FPGA神经网络实现 有效资源利用的多路复用“,IEEE 神经网络交易,18,2,2007,pp.880- 888.

【4】 N. M. Botros,M。Abdul-Aziz,“硬件实施 现场可编程的人工神经网络设计 门阵列(FPGA)“,IEEE工业交易 电子学,41,6,1994,pp.665-667.

【5】T. Orlowska-Kowalska,M。Kaminski,“FPGA实现 多层神经网络在速度估计中的应用 “双驱动系统”,IEEE工业交易 信息学,2011年7月3日,第436-445页.

【6】 P. K. Meher,S。Chandrasekaran,A。Amira,“FPGA实现 用有效和灵活的Systolization实现FIR滤波器的研究 分布式算术“,IEEE信号交换 Processing,56,7,2008,pp.3009-3017.

【7】 K. N. Macpherson,R。W. Stewart,“快速原型 - 区域 用于高速FPGA实现的高效FIR滤波器“, IEE会议录─视觉,图像和信号处理, 153,6,2006,pp.711-720.

[8] D. Kim,“模糊逻辑控制器的实现” 重新配置FPGA系统“,IEEE Tran sactions on Industrial Electronics,47,3,2000,pp.703-715.

【9】 T. L. Singal,模拟和数字通信,Tata Mc Graw Hill,2012.

【10】 M. Sonzem,A。Akbal,“基于FPGA的BASK和BPSK 使用VHDL的调制器:设计,应用和 不同调制器的性能比较 算法“,国际计算机应用杂志 卷。 2012年3月42日第13号.

图 3:BPSK调制器的仿真结果

图 4:QPSK调制器的仿真结果

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[18963],资料为PDF文档或Word文档,PDF文档可免费转换为Word

课题毕业论文、外文翻译、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。