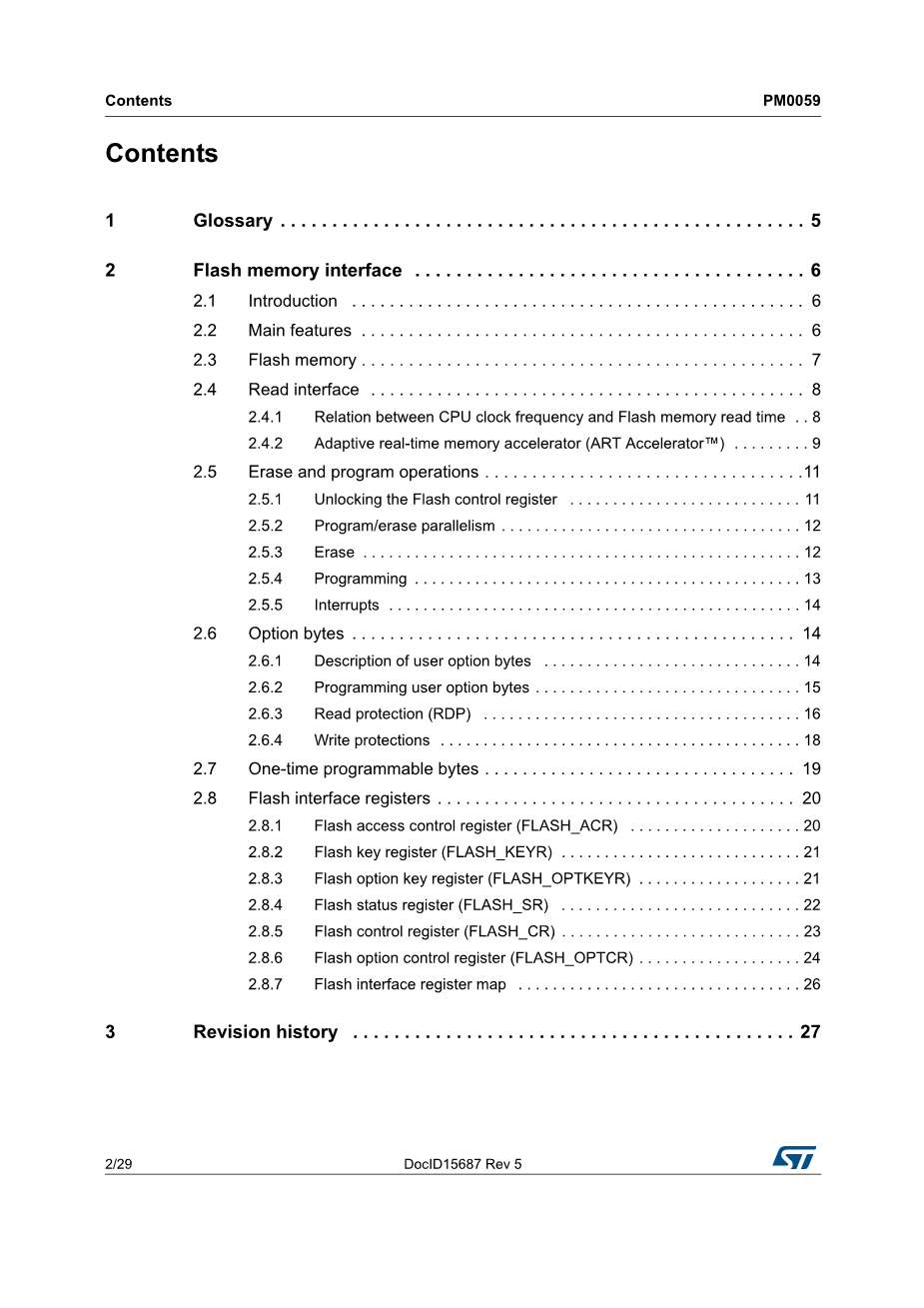

英语原文共 29 页,剩余内容已隐藏,支付完成后下载完整资料

pm0059编程手册

stm32f205 / 215 / 217,学位论文Flash编程手册

介绍

本编程手册介绍了如何计划stm32f205 / 215 / 217微控制器的闪存STM32F207。为方便起见,这些将被称为在本文档的其余部分stm32f20x和stm32f21x除非另有规定。

stm32f20x和stm32f21xembedded闪存可以在电路编程或应用程序使用的程序。

在电路编程(ICP)的方法是用来更新的闪存的整个内容,使用JTAG,社会福利署协议或引导装载机加载到微控制器的用户应用程序。ICP提供快速和高效的设计迭代和消除不必要的包装处理设备或镶嵌。

在ICP方法相比,在应用程序编程(IAP)可以使用任何通信接口由微控制器支持(I /操作系统,USB,可以,UART,2C,SPI等)下载到内存编程数据。随着IAP,闪存可以重新编程,而应用程序正在运行。然而,应用程序的一部分已被先前编程的闪存中使用ICP。

Flash接口实现的指令访问和数据基于AHB总线存取协议。它实现了一个预取缓冲区,加快了CPU代码的执行速度。它还实现了必要的逻辑进行快闪记忆体操作(程序/擦除)。程序/擦除操作可以在整个产品电压范围内进行。读/写保护和选项字节也实现。

1词汇

本节简要介绍了本文档中使用的缩写和缩写:

0the CPU为核心,集成了两个调试端口:

–JTAG调试端口(jtag-dp)提供了一种基于联合测试行动小组5针标准接口(JTAG)协议。

–SWD调试端口(swd-dp)提供两(时钟和数据)接口基于串行调试(SWD)协议。

对于JTAG和社会福利署的协议,请参阅皮质M3技术参考手册

0word:32位长度的数据/指令。

0half词:数据/指令为16位长度。

0byte:8位长度的数据。

0double词:64位长度的数据。

0iap(应用编程):IAP编程快闪记忆体的一个微控制器在用户程序运行的能力。

0icp(在线编程):ICP是一个单片机的程序使用JTAG闪存的能力,社会福利署协议或引导装置,安装在用户板的应用。

0i代码:该总线是连接CPU核心的指令总线的Flash教学界面。在此总线上执行预取。

0d代码:该总线连接d-code总线(字面负载和调试访问)的CPU的Flash数据接口。

0option字节存储在闪存产品配置位。

0obl:选项字节装载机。

0ahb:先进的高性能总线。

0cpu:指以Cortex-M3内核。

2闪存接口

2.1introduction

Flash存储器接口管理CPU和AHB i-code d-code访问1字节(64 kbittimes;128位)闪存。它实现了擦除和编程闪存操作和读写保护机制。

闪存接口加速代码执行与系统的指令预取和高速缓存行。

2.2main特征

0flash存储器读操作

0flash存储器编程/擦除操作

0read /写保护

在i-code 0prefetch

对128位064 i-code缓存线

在128位08级缓存线光栅码盘

图1显示了系统架构内的闪存接口连接。

2.3flash记忆

闪存具有以下主要特点:

0capacity最多1字节

0128位宽数据读取

0byte、半字、字和双字写

0sector和批量擦除

0memory组织

闪存的组织如下:

–内存块包含16字节64字节4部门,1部门,7部门和128字节

系统内存用于引导设备在系统内存启动模式。

这个区域是保留给意法半导体和包含引导程序是用来编程闪存通过以下接口:USART1,usart3,CAN2,USB OTG FS模式(DFU设备:设备固件升级)。引导程序是由ST编程时,该设备的制造,并防止杂散写/擦除操作。

512 OTP(一次性可编程)字节的用户数据

OTP区域包含16个额外的字节用来锁定相应的OTP数据块。

选项字节:读写保护,博尔级,看门狗软件/硬件和复位时,该设备处于待机或停止模式。

0low功率模式(详见功率控制(PWR)的参考手册)

2.4read接口

CPU的时钟频率和闪存的读取时间之间的2.4.1relation

从闪存正确读取数据,等待状态的次数(时间)必须正确编程闪存的访问控制登记(flash_acr)根据CPU的时钟频率(HCLK)和器件的电源电压。表3显示了等待状态与CPU时钟频率之间的对应关系。

预取必须禁用时,电源电压低于2.1 V

1。如果irroff设置VDD上stm32f20xx设备,这个值可以降低到1.65 V时,器件工作在降低的温度范围。

复位后,CPU时钟频率为16 MHz和0等待状态(WS)是配置在flash_acr登记。

强烈建议使用下列软件序列来调整等待状态的数量,用CPU频率访问闪存。

增加CPU频率

1。程序等待国家的flash_acr登记延迟位新号码

2。检查等待状态的新号码是考虑到通过阅读flash_acr登记访问闪存

3。在rcc_cfgr登记写西南位修改CPU的时钟源

4。如果需要的话,在rcc_cfgr写作修改CPU时钟分频器HPRE位

5。检查新CPU的时钟源或/和新的CPU时钟分频器的值是通过读取时钟源状况考虑(申位)或/和AHB预分频器值(HPRE位),分别在rcc_cfgr登记。

降低CPU频率

1。在rcc_cfgr登记写西南位修改CPU的时钟源

2。如果需要的话,在rcc_cfgr写作修改CPU时钟分频器HPRE位

3。检查新CPU的时钟源或/和新的CPU时钟分频器的值是

通过读取时钟源状况考虑(申位)或/和AHB

预分频器的值(HPRE位),分别在rcc_cfgr登记

4。程序中的延时等待状态flash_acr位新号码

5、检查新的等待状态是用来访问闪存的

阅读flash_acr登记

注意:CPU时钟配置或等待状态(WS)配置的更改可能不是有效的

笔直走。要确保当前CPU时钟频率是你所拥有的

配置,您可以检查AHB预分频因子和时钟源的状态值。以

确保您已编程的WS的数量是有效的,您可以阅读

flash_acr登记。

2.4.2adaptive实时内存加速器(ART加速器trade;)

专有的自适应实时(艺术)内存加速器是行业标准的ARM STM32reg;皮质trade;-M3处理器优化。它平衡的ARM Cortex-M3的固有的性能优势,闪存技术,通常需要较高的操作频率的处理器在等待闪存。

释放150 DMIPS的处理器性能,加速实现指令预取队列和分支缓存提高程序执行的速度从128位闪存。基于CoreMark基准,取得的业绩得益于艺术加速器相当于0等待状态的程序执行从Flash存储器在CPU频率高达120 MHz。

指令预取

每个闪存读操作提供128位从四位或8指示的16位的指示,根据程序启动。因此,在顺序代码的情况下,至少需要四个CPU周期执行以前的读取指令行。在i-code总线预取可以用来读取下一指令线从闪存而电流指令线是由CPU要求。预取是由设置在flash_ ACR登记的prften点启用。如果访问闪存需要至少一个等待状态,则此功能非常有用。

图2显示的顺序执行32位指令和无预取3时WSS需要访问存储器。

图2。顺序32位指令执行

当代码是不连续的(分支),指令可能无法在预取指令线,目前使用的指令线或。在这种情况下,根据循环次数的惩罚至少等于等待状态的数目。

指令高速缓冲存储器

为了限制由于跳转而丢失的时间,可以在指令高速缓冲存储器中保留64行的128位。这个功能可以通过设置指令缓存启用启用(ICEN)位在flash_acr登记。每一次错过发生(请求的数据不在预取指令线或在指令高速缓冲存储器目前使用的指令线),线读复制到指令高速缓冲存储器。如果指令高速缓存内存中包含的某些数据由CPU请求,则不提供任何延迟。一旦所有的指令高速缓存线已满,LRU(最近最少使用)政策是用来确定线在指令缓存替换。在包含代码的循环的情况下,此功能特别有用。

数据管理

文字池取通过d-code总线从闪存的CPU流水线的执行阶段。CPU管道因此中断,直到所请求的文字池提供。限制因文字池,通过访问AHB总线d-code优先访问通过AHB总线指令i-code。

如果一些文字池中经常使用的数据缓存,可以通过设置数据缓存启用启用(DCEN)位在flash_acr登记。此功能像指令高速缓存内存,但保留的数据大小仅限于8行的128位。

注:在用户配置部门的数据是不可。

2.5erase和程序操作

任何闪存编程操作(擦除或程序),CPU的时钟频率(HCLK)必须至少为1 MHz。如果闪存操作期间发生设备复位,则不能保证闪存的内容。

在对闪存的写/擦除操作中,任何试图读取闪存会导致总线失速。一旦程序操作完成,读取操作将被正确处理。这意味着代码或数据提取不能执行,而写/擦除操作正在进行中。

2.5.1unlocking闪光控制登记

复位后,写的不是在闪光控制登记允许(flash_cr)保护

闪存对可能的不必要的操作,例如,例如,电

扰动。下面的序列用于打开这个寄存器:

1。在闪光钥匙登记写KEY1 = 0x45670123(flash_keyr)

2。在闪光钥匙登记写KEY2 = 0xcdef89ab(flash_keyr)

任何错误的序列将返回一个总线错误和锁定flash_cr登记直到

下一个复位。

的flash_cr登记可由软件再次锁定在锁位设置

flash_cr登记。

注:本flash_cr登记不可写模式时,在flash_sr BSY位

寄存器设置。任何试图把它与BSY位设置将导致AHB总线失速

直到BSY清零。

2.5.2program/erase并行

平行度的大小是通过在flash_cr登记的psize场配置。它代表每次写入操作发生在快闪存储器时要编程的字节数。psize是由电源电压和外部供应是否VPP的使用或不限。因此它必须被正确地配置在flash_cr登记之前,任何的编程/擦除操作。

快闪记忆体擦除操作只能由部门,银行或整个快闪记忆体(质量擦除)。擦除时间取决于psize程序价值。关于擦除时间的更多细节,请参阅设备的电气特性部分数据表。

表4。程序/擦除并行

1。如果irroff设置VDD上stm32f20xx设备,这个值可以降低到1.65 V时,器件工作在降低的温度范围。

注意:任何程序或擦除操作开始与不一致的程序并行/电压范围

设置可能会导致不可预知的结果。即使随后的读取操作表明

逻辑值被有效地写入内存,这个值可能不被保留。

使用VPP,外部高压电源(8 V和9 V)之间必须应用到VPP

衬垫.外部电源必须能够维持这个电压范围,即使直流

消费超过10毫安。建议限制加上初始编程使用

工厂线。VPP供应的实施不应超过一个小时,否则

闪存可能损坏。

2.5.3擦除

闪存擦除操作可以在扇区级或整个闪存(质量擦除)。质量擦除不影响OTP扇区或配置扇区。

扇区擦除

要清除扇区,请按照以下步骤操作:

1。检查没有闪存的操作是通过检查在flash_sr BSY位进行登记的

2。设置服务点和选择部门(从12部门在主内存块)你希望擦除(SNB)在flash_cr登记

3。设置开始点的flash_cr登记

4。等待被清除BSY位

块擦除

要执行质量擦除,建议以下顺序:

1。检查没有闪存的操作是通过检查在flash_sr BSY位进行登记的

2。设置在flash_cr MER点登记

3。设置开始点的flash_cr登记

4。等待被清除BSY位

2.5.4programming

标准的编程

闪存编程顺序如下:

1。检查没有主要的闪存操作是通过检查在flash_sr BSY位进行登记的。

2。设置在flash_cr登记PG位

3,执行数据写入操作(s)到所需的内存地址(主内存块或OTP区域内):

–字节访问在x8并行的情况

–半字访问在x16并行的情况

–字访问在X32并行的情况

–双字访问在x64并行的情况

4。等待被清除BSY位

注:连续写操作是可能的,而不需要擦除操作时

将位从“1”改为“0”。

写 1 需要快闪记忆体擦除操作。

如果同时要求擦除和程序操作,则擦除操作是

首先进行。

编程错误

不允许将数据编程到将跨越128位行边界的闪存中。在这样的情况下,写操作是不执行,一个程序对齐错误标志(pgaerr)设

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[613923],资料为PDF文档或Word文档,PDF文档可免费转换为Word