英语原文共 5 页,剩余内容已隐藏,支付完成后下载完整资料

窗体顶端

窗体顶端

基于FPGA的改进型DDS函数发生器的实现

窗体底端

Eltimir Chavdarov Stoimenov, Georgy Slavchev Mihov , Ivailo Milanov Pandiev

Technical University of Sofia, Faculty of Electronic Engineering amp; Technologies

摘要:窗体顶端

本文提出了一种基于现场可编程门阵列的改进型直接数字合成函数发生器。 直接数字合成是从参考频率源产生多个频率的方法。 该模式是两个分离模块的组合--一个配有FPGA Spartan-3A(来自赛灵思公司)的评估板和一个包含数模转换器和输出放大器的印刷电路板。现有的FPGA合成正弦或其他信号的研究都是以数字形式。 合成本身是通过一个基于正弦波波形的样本查找表来实现的。 并行接口用于将信息从FPGA传输到14位数模转换器。此外,还集成了双路低通滤波器,可变增益放大器和输出放大器,以使输出信号在整体频率范围内。 所设计的DDS发生器的参数可以由个人计算机通过USB接口控制。

关键词:混合信号系统,直接数字合成,函数发生器,FPGA,DAC,可变增益放大器

窗体顶端

I.引言

窗体底端

窗体顶端

直接数字合成(DDS)类的发生器是众所周知的,因为它的宽频带和高分辨率。 通常,这些器件从一个或多个参考频率产生多个频率。 它们由一个计数器(也称为“相位累加器”),即每个时钟周期进行累加一次,以及用于存储一个周期正弦波的采样信息的查找表(LUT)。 来自相位累加器的数字作为LUT的输入地址。 随着数字递增(及地址),在LUT的数据输出端将产生正弦波。数模转换器(DAC)和一些额外的模拟电路用于模拟信号的产生。

此外,由于数字式DDS系统非常适用于类似FPGA这样可重编程的系统。 FPGA技术提供了易应用和全面的软件控制系统设计。同时使用预编好的IP内核,大大减轻了设计负担。FPGA具有一些缺点,与专用集成电路(ASIC)相比,如缩小带宽和更高的组件数量。

窗体底端

窗体顶端

在我们早期的工作中,我们设计了一个基于FPGA和可编程片上集成系统的类似DDS的发生器。 这种实现方式有较低的模块数和较高的噪声抑制。 然而,输出信号的带宽减小是一个根本的限制。为了克服这个障碍我们决定避免在设计中使用PSoC。 一种使用外部高速DAC的新观点被应用在本设计中。 接下来的目标计划是:输出信号形式:正弦波,

三角波,方波;频率范围:0—2 MHz; 频率分辨率:1Hz; 幅度分辨率:10mV在plusmn;200mV到plusmn;2V之间和1mV在plusmn;20mV到plusmn;200mV; 输出信号幅度:plusmn;10 V; 直流偏移调谐分辨率:1 mV; DC偏移值:plusmn;1 V; THD:le;0.1%(-60dBc),SNR:ge;60dB;PC连接:通过标准USB端口。

窗体顶端

II. DDS函数发生器的设计与实现

系统采用自顶向下的设计方法。 该方法的起点是第一节结尾讨论的目标。首先,合成框图。 接下来,产生示意图并计算适当的值。 最后,实现了一个原型,并进行了实验研究。将研究结果与一开始所定义的目标进行比较。

A.框图

窗体底端

窗体底端

窗体顶端

系统的框图如图1所示。 信号流由“DDS”模块产生数字正弦波开始。 来自模块的16位宽输出信息被传递到14位DAC处理。 前两个低有效位(LSB)被截断。 转换后,模拟信号通过“重构低通滤波器”块进行滤波。 此外,信号由电压控制放大放大器(VCA)。 信号的放大和DC偏移由“增益控制”和“直流偏移”块标识。 最后,“输出级”通过同轴线传输信号。

图1 DDS函数发生器框图

B.原理图综合

B.1 DDS核心

该模块应能够以数字形式产生正弦波信号。 频段应为0至2 MHz,分辨率为1 Hz。 如已经讨论的那样,该模块将在FPGA中实现。 我们将使用Xilinx Spartan-3A评估套件进行开发。该套件提出了以下重要的参数:

窗体顶端

赛灵思XC3S400A-4FTG256C Spartan-3A FPGA;

16 MHz系统时钟;

USB连接器;

窗体顶端

此外,我们还将利用Xilinx的DDS预写IP内核进行DDS核生成。 IP内核需要一些输入参数才能生成DDS内核。 第一个参数是IP时钟信号(DDS_CLK)。 我们会将此参数设置为尽可能高,以便我们使用主板系统时钟。

DDS_CLK=16MHz (1)

窗体顶端

其次,必须定义输出数据分辨率。更好的是,应该使用合理的值。只需要足够的相位分辨率,使得截断误差小于DAC的分辨率。 这要求LUT具有比DAC多两位的相位分辨率

Output resolution=16-bit (2)

第三,需要频率调谐字宽度。 系统的频率分辨率(FR)可以通过以下方程定义:

(3)

(4)

窗体顶端

其中N是频率调谐字宽度。 根据我们的目标FR = 1 Hz,因此

窗体底端

N=24-bit (5)

B.2数模转换器

该模块在设计中具有关键作用。 必须能够高精度地以模拟形式转换数字波形。 DAC有两个主要参数-- 输入分辨率和采样频率。分辨率可以通过以下基本方程推断:

SNR=N*6.02dB 1.76dB (6)

(7)

窗体顶端

根据我们的目标SNRgt; 60dB,但是我们将使用更高的SNR = 70dB的值。 经过计算,我们推断

(8)

窗体顶端

根据经验,采样时钟频率(DAC_CLK)应为BW的10倍。我们可以定义DAC_CLK = 10*2 MHz = 20 MHz。对于硬件便利,我们将使用Avnet开发套件的时钟信号:

CLK_DAC=16MHz (9)

窗体底端

窗体顶端

考虑到这些因素,我们选择德州仪器的THS5671A作为我们的需求。 IC提供以下主要功能:

125 MSPS更新率;

14位分辨率;

无杂散动态范围(SFDR)到Nyquist at

40 MHz输出:63 dB;

片上1.2 V参考电压;

B.3 缓冲放大器

窗体底端

窗体顶端

该放大器应具有足够的BW和压摆率尽可能高。 为此,我们将考虑电流反馈运算放大器(CFOAs)进行设计。我们从德州仪器选择THS 3096(双运算放大器)

仪器具有以下参数:

压摆率:5700 V /mu;s(G = 5,Vo = 20 VPP)

带宽:160MHz(G = 5,RL =100Omega;)

输出电流:plusmn;250 mA

电源范围:plusmn;5 V至plusmn;15 V

B.4低通滤波器

窗体顶端

众所周知,设计滤波器是混合信号系统中最困难的部分之一。 滤波器应通过有用的信号并消去不需要的频率分量。 正如我们在目标中所定义的输出信号的BW应高达2 MHz一方面,LPF的转角频率应至少比BW大3倍,所以

f-3dB=3*BW=6MHz (10)

窗体顶端

另一方面,奈奎斯特频率以上的任何频率分量应尽可能的衰减。 如果我们考虑

(11)

窗体底端

窗体顶端

并且假定我们将获得具有40dB/ dec的滤波器,用于我们将获得的转角频率

f-3dB=800KHz (12)

窗体顶端

现在我们可以合成滤波器拓扑。 为了简单起见,我们将使用二阶无源RC滤波器,后跟缓冲放大器。

对于转弯频率我们有:

(13)

窗体顶端

如果我们设置R = 1kOmega;和f-3dB = 100 kHz的值,可得电容为:

(14)

图2 DAC和LPF频率传递函数。

窗体顶端

在图 2显示了DAC和LPF滤波器的频率传递函数。可以看出,DAC传递函数遵循在时钟频率下的零点及其倍数响应。

B.5 VCA

窗体底端

窗体顶端

VCA模块负责将输出信号放大到所需值。 其增益由增益控制块产生的电压控制。 VCA模块应具有增益控制带宽(BW)

(15)

窗体顶端

此外,压摆率应尽可能高(至少50 V /mu;s)。 增益控制方法应为直流电压。德州仪器的VCA810似乎是一个适当的选择。 IC提供以下重要特征:

高增益调节范围:plusmn;40 dB

恒定带宽与增益:35 MHz

低输出直流误差:lt;plusmn;40 mV

高输出电流:plusmn;60 mA

B.6 输出部分

输出级应该能够输出通过具有足够功率的同轴电缆发出信号。 它输出阻抗必须为50Omega;,输出信号摆幅分为两个级别,第一个是从plusmn;20 mV到plusmn;200 mV,第二个为plusmn;200 mV至plusmn;2 V(在RL =50Omega;)。 输出阶段的实现将依赖于“缓冲放大器”部分讨论的CFOA运算放大器。

B.7直流偏置和增益控制

窗体顶端

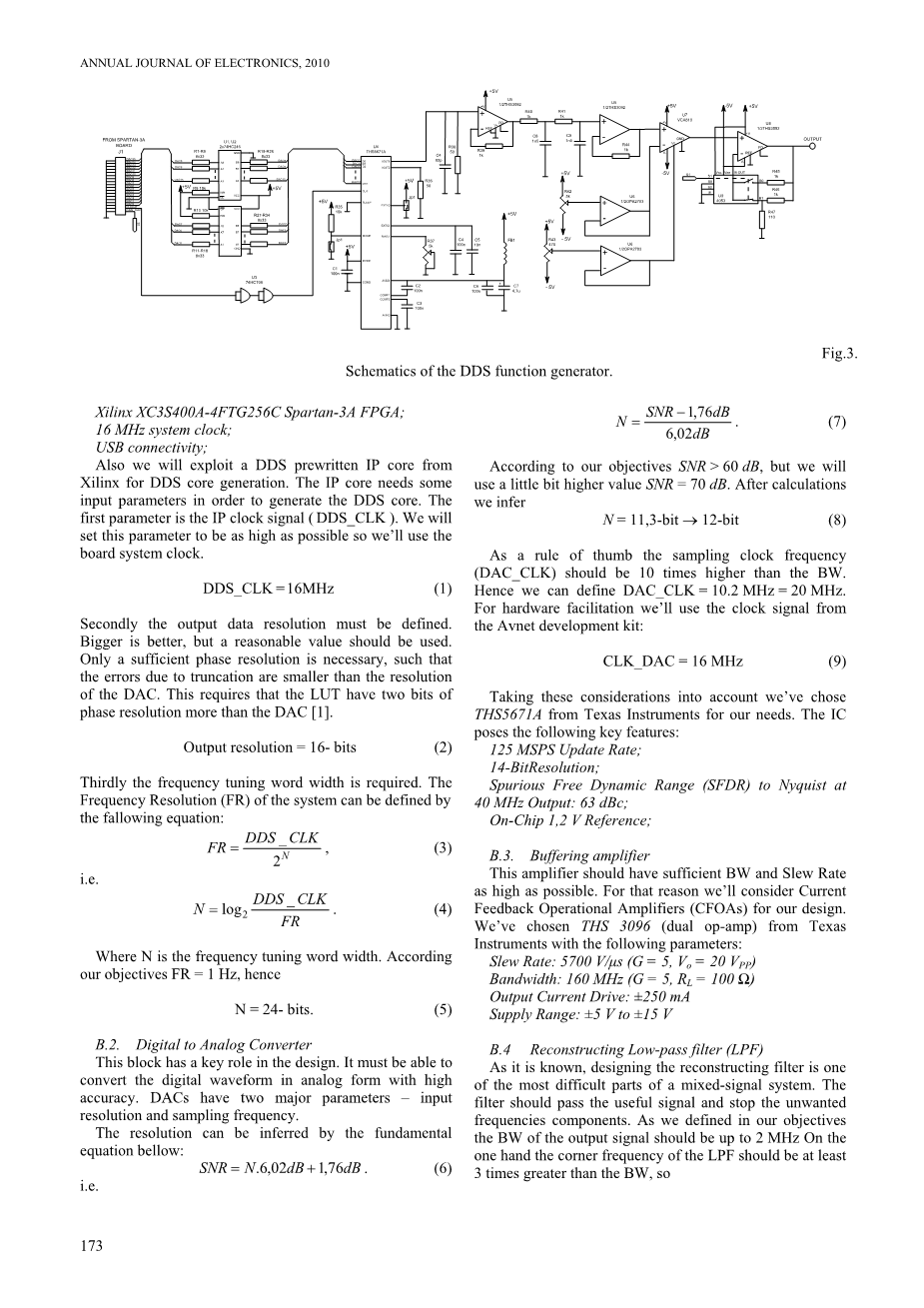

这些模块将被实现为简单的电位计。 我们将在进一步的研究中寻找更复杂的解决方案。 输出级也只有一个范围从plusmn;20 mV到plusmn;200 mV。图3表明合成图。

窗体顶端

图3 DDS函数发生器合成图

窗体顶端

Ⅲ. 实验测试

窗体顶端

图4 DDS发生器的输出信号为A = 1 V和f = 1 kHz:a)正弦波; b)三角波; c)方波。

窗体顶端

本节介绍了实验研究中的一些示波图。 使用以下技术设备:赛灵思Spartan - 3A评估套件; Tektronix 1002B示波器(示波器设置:AC模式和1X探头衰减); 个人电脑。

窗体顶端

图4显示了正弦,三角和平方输出信号。 信号幅度和频率分别为1 V和1 kHz。 也是一个正弦曲线的FFT分析.

图5 正弦输出信号的快速傅里叶变换

窗体顶端

信号如图5所示。 基频在1 kHz时清晰可见。 此外,还出现了一些其他谐波(1 kHz和2 kHz),但它们比基准谐波低30 dB。分析结果后,可以做出所需和实现结果之间的比较表(表1)。

表1 实验结果与早期工作结果的比较

|

参数 |

早期值 |

当前值 |

|

输出信号波形 |

正弦波,三角波,方波 |

正弦波,三角波,方波 |

|

频带 |

0-200Hz |

0-100kHz |

|

频率分辨率 |

8-bit |

24-bit |

|

幅值分辨率 |

4 bit |

8 bit |

|

输出信号幅值 |

0-3.3V |

plusmn;5V |

|

谐波失真 |

1% |

0.1% |

|

电脑连接 |

通过标准USB端口 |

通过标准USB端口 |

IV. 结论

窗体顶端

本文提出了DDS函数发生器的改进电路。 该电路通过FPGA使用FPGA提供的功能实现。标准可编程模拟处理IC用于形成输出电气参数。 在最近的出版物中,作者提出了一种仅在FPGA和PSoC IC实现的DDS函数发生器,并在0到200 Hz的频率范围内提供正弦,三角和方波输出信号。 在此参考文献中,我们引入了DDS发生器的改进电路,其具有更高的

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[27293],资料为PDF文档或Word文档,PDF文档可免费转换为Word

课题毕业论文、外文翻译、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。