英语原文共 6 页,剩余内容已隐藏,支付完成后下载完整资料

基于FPGA的高精度数字频率信号源

摘要

本文介绍了DDS技术的实现方法,并对其技术特点进行了分析。 根据其特点,设计了基于FPGA的高精度数字频率信号源。

仿真结果表明,与传统信号源相比,依靠FPGA DDS方法实现的信号源具有精度高,开关速度快等优点,可以满足测试设备的发展趋势。

关键词:DDS ,信号源,FPGA

- 简介

信号源主要用于为被测设备提供各种基本信号,便于测试和分析他们的性能,是最重要和必需的设备,广泛应用于电子测试,测量和航空航天的科学研究等许多领域。目前,信号源的价格主要与其波形产生的频率精度有关。本文介绍了一种基于FPGA的直接数字频率合成信号源,具有精度高,波形多,体积小,成本低等优点,同时适用于测试设备数字化的发展趋势 。

- 直接数字频率合成技术

DDS(直接数字频率合成)技术是随着数字集成电路的出现和微电子技术的发展而出现的一项新技术。 采用数字采样存储技术,从相位角度进行频率合成,具有很好的优点,转换时间快,频率精度分辨率高。DDS专用芯片内置高速DA转换器,通过极高的采样时钟频率将参考源转换为正弦波。在性能方面,它具有相当大的优势,具体体现在带宽范围宽,频率转换时间短,频率分辨率高,输出相位连续,可以产生正交信号等多种调制信号。它采用了数字化控制技术,这意味着它不需要人工系统来调节,从而很方便地提供所需频率的信号。它是新一代的频率合成器,从测量仪器到无线和卫星通信领域,都有广泛的应用。

目前,许多大型芯片设计制造厂商纷纷推出采用先进CMOS工艺的高性能,多功能DDS芯片,为电路设计人员提供了多种选择。 但在某些情况下,专用DDS芯片在控制方式,工作频率,速度等方面远远落后于系统的要求,所以借助高性能FPGA器件设计满足要求的DDS电路是一个非常合理的解决方案。

2.1直接数字合成技术原理

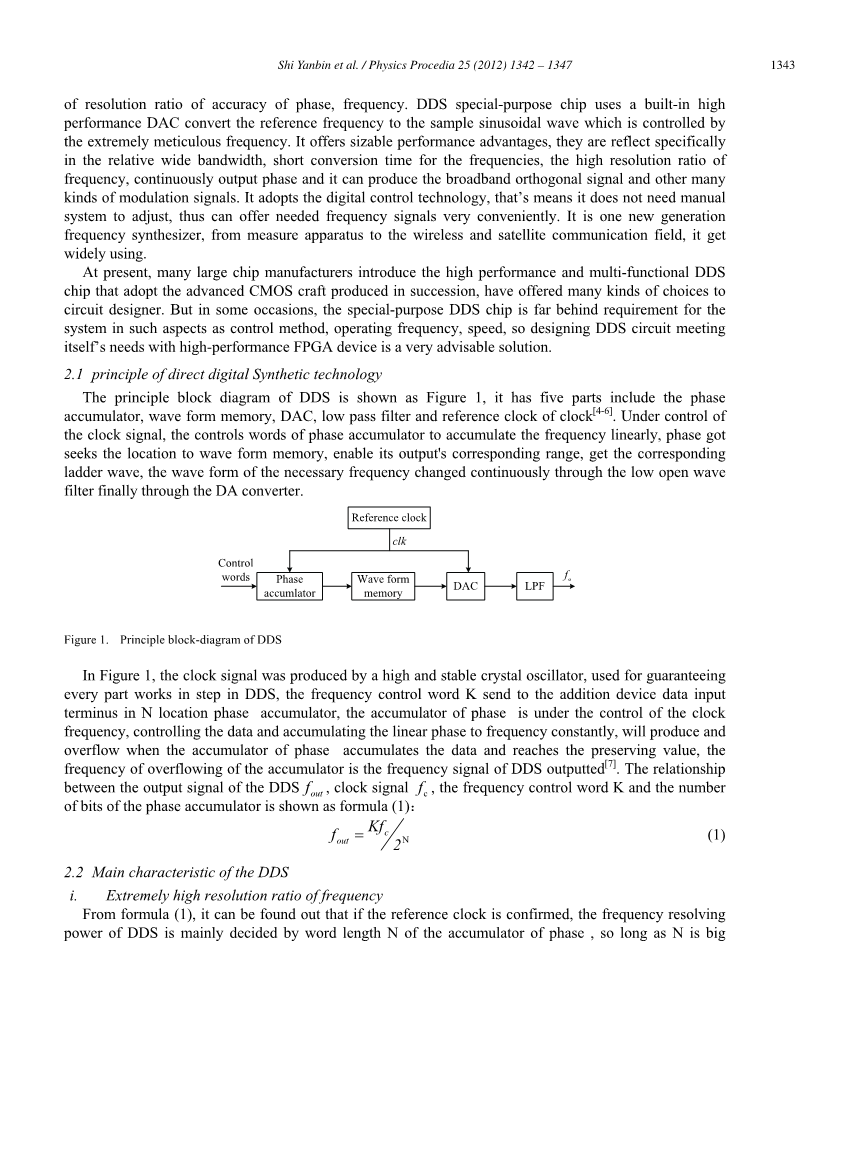

DDS的原理框图如图1所示,包括相位累加器,波形存储器,数模转换器,低通滤波器和系统参考时钟五个部分。在时钟信号的控制下,相位累加器的控制字线性地累积频率,通过相位寻址波形存储器的位置,使其输出的相应存储的数据,经过DA转换器的转换,获得相应的梯形波,最后通过低通滤波器获得连续变化的波形频率。

图1:DDS的原理框图

在图1中,在图1中,时钟信号由稳定的高频晶体振荡器产生,用于保证DDS中每部分模块正常工作,频率控制字K发送到N位长的相位累加器中的数据输入端,相位累加器在时钟频率的控制之下,控制数据并线性累积相位,当相位累加器累积数据并达到预设值时,将产生和溢出,累加器溢出的频率值是DDS输出的频率信号,关于DDS输出频率,时钟频率,频率控制字和相位累加器位长之间的关系如公式(1)所示:

(1)

2.2 DDS的主要特征

i. 极高的频率分辨率

从公式(1)可知,可以看出,如果参考时钟在确定的情况下,DDS的频率分辨率主要由相位累加器的字长决定,只要足够大,可以获得足够高的频率分辨率。当K= 1时,DDS产生的最低频率被称为频率分辨率,

(2)

举个例子,如果DDS系统的参考时钟频率为=40MHz,N=32,所以可以达到0.9*10-5Hz。

ii. 极短的频率转换时间

由图1可以知道,DDS是个开环系统,这种结构确定了DDS的频率转换时间是频率控制字的传输时间与ROM的响应时间之和。在FPGA和专用的DDS器件中,由于采用高速组装线结构,变频时间可以达到ns级。

iii. 当频率捷变时相位变化连续

在跳频通信系统中,传统的频率合成技术在实现频率捷变存在一些困难。 但在DDS中,输出信号改变的信号并不是两个不同信号,而是相同信号的相位增益发生变化,因此输出信号的相位是连续的。

iv. 任意波形输出

相位累加器相位寻址输出的波形由DDS中存储在波形存储器中的数据决定。如果存储在波形存储器中的高频信号频率小于采样频率的一半,那意味着只要存储的数据符合采样定理,则该波形就可以通过DDS技术产生,并且因为DDS是模块结构,所以只要改变波形存储器内部的存储数据,就可以利用DDS产生任意波形,比如正弦波、方波、三角波、锯齿波等波形。

- 信号源

根据以上所述DDS技术的主要特点,本设计选用FPGA的ACEXEP1K100型号芯片,其最大门电路数为257000,典型门电路数为10万,具有4 992个逻辑单元,嵌入12个系统块, 总RAM寄存器为49 152,最大用户I / O引脚数为333,用于实现许多高精度的数字信号源。

基于查找表(LUT)的ACEX可编程逻辑器件(PLD)系列为成本敏感的卷驱动应用提供了价值和不错的性能。通信领域中消费者的理想选择是电缆调制解调器,xDSL调制解调器,低成本交换机和路由器等。ACEX设备具有专用集成电路(ASIC)和专用专用产品(ASSP)的低成本优势,还具有快速上市时间和可编程灵活性的优点。 ACEX设备提供在线可重新配置(ICR)的功能,通过允许设计人员快速实施完整的设计版本,降低了成本。这些设备得到了Altera公司强大的软件支持和预优化的知识产权,进一步缩短了上市时间。这些产品可以设计,修改,发布和更新,降低操作的复杂性。

高性能,通过卷驱动的电信产品在现实中不可或缺,需要在性能和价格之间找到平衡。ACEX设备满足这些要求。尽管价格低廉,但ACEX设备的系统性能可以达到100MHz以上的速度,而且误差最少。先进的软件拟合技术的布局和布线设计,实现了ACEX互连架构内加速设计的性能。

3.1 波形存储模块设计

正弦波信号是测试仪器中最常用的基本信号。本文以正弦信号为例论述设计波形存储模块的过程。如图2所示,它是波形存储模块的顶层综合图。应首先建立数据源文件,用C或MATLAB语言对一个周期的正弦连续信号进行采样,采样深度为2048个点,这意味着波形存储器的寻址范围为0〜211,通过QUARTUS开发软件将*.HEX文件加载到FPGA“tool MegaWizard Plug In Manager”中,根据精度要求设置存储器的存储深度和字长,这样就可以得到波形存储器模块。如图2所示,数据存储器寻址范围为2048,字长为8。将这些2048个8位正弦数据写入ROM。在文献中提到使用不同的频率控制字K控制相位累加器的相位增加,这种方法导致在不同频率控制字的情况下输出信号的精度变化,所以在本设计中使用频率控制字K来控制分频装置的分频系数,由此读取图2所示的正弦波数据存储器“inclock”端口输出的数据,可以保持输出信号的相位精度和连续性。

图2:波形存储器的顶层综合图

3.2 任意波形信号源

根据上述分析,理论上可以发现,如果不同的数据文件存储在ROM中,则DDS可以形成任意波形的信号源。正弦波形是用于测试和检查的最重要的参考信号之一,为了节省芯片的资源,可以使用正弦波形的周期性,因此可以节省ROM资源。另外,调制信号设备常用的信号形式测量,也用正弦波设计计数。基础的调制信号种类也是基于这个原理。

- 仿真结果

基于正弦信号,可以实现高精度正弦移动信号,例如PSK,FSK,ASK等信号,这里详细介绍PSK信号的生成过程。其他信号可以由这种方式得到。首先,在QUARTUS中设置ROM存储器存储2048个8位数据,并将周期性正弦采样波数据顺序存储到该ROM中,当CLK上升和改变时读取数据,然后将ROM的地址加1,从ROM一个一个读取数据,差异是sin1第一个地址是“00000000000”所以从0ordm;相位读取数据,但SIN2的第一个地址为“10000000000”,所以从180ordm;相读取数据,保证两个正弦波信号SIN1和SIN2之间的相位差在任意时间都为180ordm;。当INPUT为“1”时,输出SIN1; 并且当INPUT为“0”时,输出SIN2,PSK的波形调制如图所示。以下的程序是一些主要的VHDL语言。

signal address1: STD_LOGIC_VECTOR(10 DOWNTO 0): =' 00000000000';

signal address2: STD_LOGIC_VECTOR(10 DOWNTO 0) : =' 10000000000';

PROCESS(clk, input)

BEGIN

if (clk1event and clk1 =1) then

address1lt; =address1 1;

address2lt; =address2 1;

end if;

if(input =1) then

sinoutlt; =sin1;

else

sinoutlt; =sin2;

end if;

end process;

图片4-6分别是FSK,AM,三角波和锯齿波模拟图。设计方法与PSK信号相似,本文不提供详细的实现方法。

图3:PSK仿真

图4:FSK仿真

图5:AM仿真

图6:三角波和锯齿波仿真

- 结论

仿真结果证明,基于FPGA的自定义信号源设计简单灵活。具有易于实现,功能多,精度高,连续性好等优点。它是设计制作信号源的新选择。

参考文献:

[1] Chen Cheng; Qin Li-tao; Su Yan-qun. Implementation of DDS Signal Source Based on FPGA, Computer and Information Technology, 2010.02

[2] YANG Xin Chun; REN Lu Juan; HUANG Yang Wen, Design of adjustable signal source based on FPGA, Microcomputer amp; Its Applications, 2010.04

[3] Zhao Jubo, Song Jie, Ding Hao, Design of signal generator based on FPGA and DDS, Electronic Measurement Technology, 2010.07

[4] ZHAI Sheng-wei; LI Ying-ying; DU Bai-sheng, Implementation of a DDS signal source based on FPGA, Electronic Design Engineering, 2009.05

[5] ZHU Yue-xiu, The Design of Standard Sine Wave Supply Using FPGA, Journal of Hangzhou Dianzi University,2009.05

[6] CHEN Bo; WANG Tie, Application of FPGA to The Wide-band Signal Source of Direct Digital Waveform Synthesis,Shipboard Electronic Countermeasure, 2010.03

[7] LIU Ning; ZHEN Guo-yong, Design of Programmable Signal Generator with High Precision based on Singlechip, Power Electronics, 200.06

[8] QI Cai-li; SONG Peng; QI Jian-zhong, Design and Implementation of Multi-channel Signal Source Based on FPGA,Radio Engineering, 2010.04

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[27650],资料为PDF文档或Word文档,PDF文档可免费转换为Word

课题毕业论文、外文翻译、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。