英语原文共 11 页,剩余内容已隐藏,支付完成后下载完整资料

IEEE超大规模集成电路(VLSI)系统,第18卷,第7期,2010年7月

异步电流模式串行通信

Rostislav(Reuven)布金,Michael Moyal,高级会员,IEEE,Avinoam Kolodny,Ran Ginosar

摘要——提出了一种用于片上通信的异步高速流水线位串行链路,替代了标准位并行链路。链接采用差动级编码的双轨(LEDR)两相异步协议,避免握手和消除每比特每比特同步,在同步串行链路,依靠复杂的时钟恢复的对比。提出了一种新的低功耗电流信号驱动和接收电路,实现了长距离极低电压下的高速通信。与此相反,以前的方法采用电压传感,从而导致更高的摆动,更高的动态功率,更短的电线或较慢的操作。异步电流模式驱动程序支持不同的数据传输速率,它消除了平衡码和忙碌的切换,防止深放电的需要。链路的数据周期时间等于单个门延迟,使65纳米技术的吞吐量达到67 Gb / s。波流水线也由异步串行电路,使高速运行。该链接是65纳米技术的SPICE模拟,使用三维电磁求解器获得的线模型。该链路相对于同步和异步比特并行通信产生更低的功率和面积,这些相对好处也与技术有关。

索引术语——串扰电流信号,LEDR、SerDes、串行通信。

- 引言

由于晶体管尺寸的缩放,VLSI数字逻辑的性能在过去几年中以指数速度增长[ 1 ]。虽然本地互连的性能也有类似的趋势,但全球线并不这样做,从延迟、吞吐量和功耗等方面对长程片上数据通信提出挑战。全球互连的高电容是导线损耗的主要来源之一,在吞吐量和功率方面导致性能下降。此外,由于片上系统(SOC)集成了越来越多的模块,片上模块间通信变得拥挤,模块必须转向串行接口,类似于从并行到串行芯片到芯片互连的趋势。

常见的同步片上并行链路(多线互连)占用大面积,高容性负载,并产生高的动态和漏电功耗和交叉耦合噪声,尤其是在远程通信是考虑过的.对于使用率较低的应用程序(例如,片上网络[ 2 ])或具有高互连拥塞(例如,路由器、交叉口交换机[ 3 ],[ 4 ]),这个问题会加剧。同步并行链路的时钟频率与时钟和数据的不确定性有关,随着链路时间的延长,时钟的不确定性越来越严重。虽然标准的同步串行链路采用与并行链路类似的时钟,但由于比特率有限,没有吸引力,新型高性能串行链路可为并行链路提供一种替代方案。

同步串行链路通常用于片外通信,其中引脚限制要求每个链路的最小数量的线路。源同步协议经常用于这些应用程序[ 5 ] [ 10 ]。串行互连的公共定时机制向传输端的数据流注入时钟,并在接收机处恢复时钟。这种时钟数据恢复(CDR)电路通常需要一个功率很低的锁相环,这可能需要很长时间才能在每个传输开始时会聚在适当的时钟频率和相位上。如果接收器和发送器在不同的时钟域中工作,则事务也必须在两端同步,从而产生额外的延迟和功率。或者,异步数据链路使用握手代替时钟。传统的异步协议是慢了needtoacknowledgetransitions [ 11 ],[ 12 ]。在[ 13 ]中,异步协议共享数据线,但它们的性能取决于线延迟。

同步串行链路通常用于片外通信,最近已经提出了限制高速串行链路,具有几个门延迟(向下到单门延迟周期)的数据周期。[ 14 ] [ 22 ]。这些快速链接采用流水线–波[ 23 ] [ 25 ],低摆幅差分信号,快速的时钟发生器和asynchronousprotocols。此外,theselinksrequirechanneloptimization支持宽带数据传输连接线。在[ 19 ]中提出了一种波前列车串行化链路。序列化程序是基于链器(类似于[ 26 ])。该链路是单端的,采用波流水线。链接数据的周

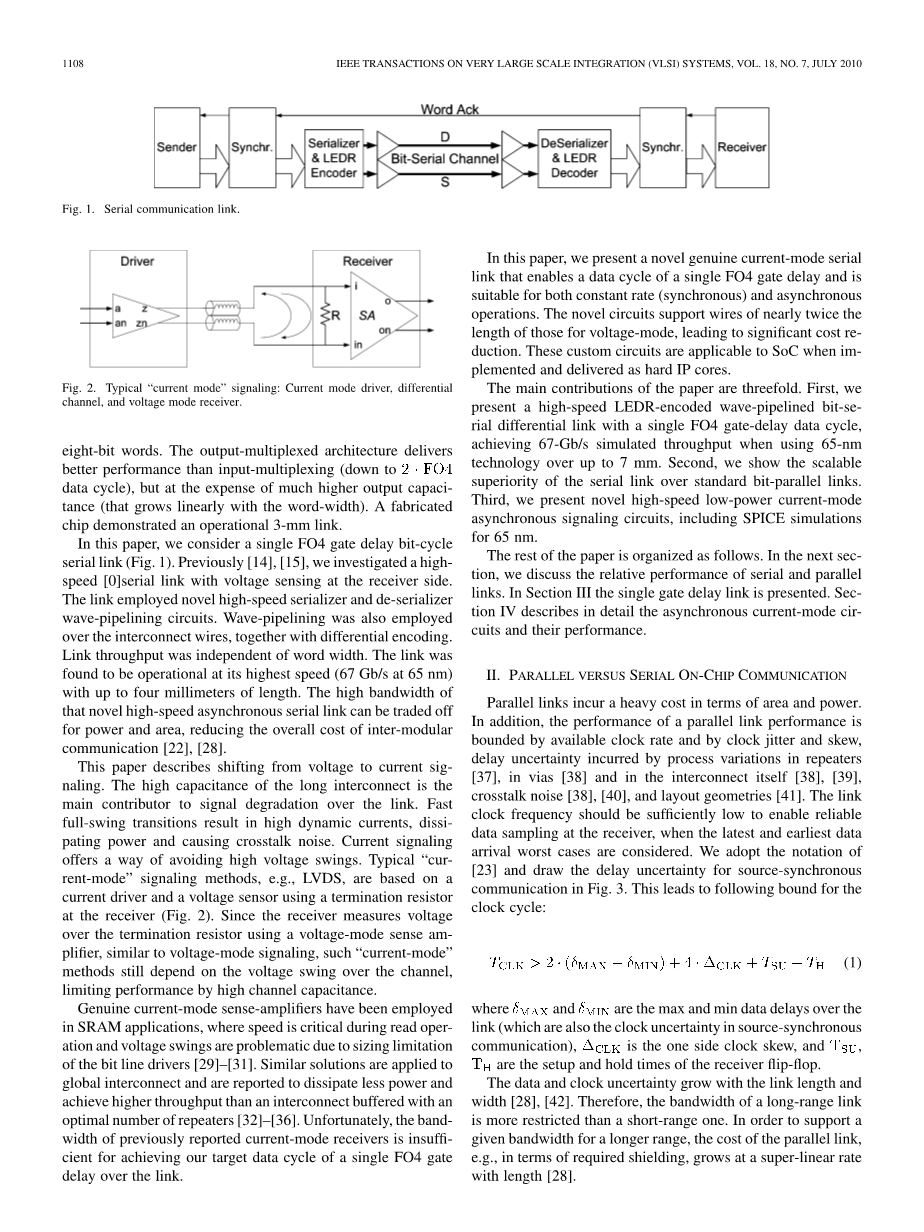

图1、串行通信链路。

期大约是7 FO4(风扇四)延迟(3 Gb/s @ 180 nm)。波流水线多路复用(WPM)路由技术是[ 20 ],[ 21 ]。WPM路由采用源同步通信,它的性能是有限的由时钟偏移和延迟的变化。采用低voltagedifferential对分散芯片串行互连是[ 17 ]和[ 18 ]的讨论,其中的数据是在没有任何关注的接收机采样同步问题。三级电压摆幅是[ 27 ],要求非标放大器。

最初为片外通信设计的电路[ 5 ],[ 10 ]被用于片内串行链路[ 16 ]。输出多路复用发射机连接到复用接收机,需要在接收机侧校准时钟。发射机和接收机都使用多相动态链路电路。该链路采用低摆动差分信令和传输。

图2。典型的“电流模式”信号:电流模式驱动器、差分通道和电压模式接收器。

八位字。输出多路复用架构比输入多路复用(向下到数据周期)提供更好的性能,但牺牲了更高的输出电容(与单词宽度成线性增长)。制造的芯片显示3mm链接操作。

在本文中,我们考虑一个单一的FO4栅极延迟点周期串行链路(图1)。以前[ 14 ],[ 15 ],我们研究了一个高速[ 0 ]串行链路与电压传感在接收端。采用新型高速串行器和解串波流水线电路。在互连线上也采用了波流水线,并与差分编码相结合。链路吞吐量与字宽度无关。该链接被发现以最高速度运行(67 Gb / s,在65纳米),长度可达四毫米。这种新颖的高速异步串行链路的高带宽可被用于功率和面积的折衷,从而降低模块间通信的总成本[ 22 ],[ 28 ]。

本文描述了从电压到电流信号的转换。长互连的高电容是链路上信号劣化的主要因素。快速全摆幅转换导致高动态电流,耗散功率和引起串扰噪声。电流信号提供了一种避免高电压波动的方法。典型的“电流模式”信令方法,例如LVDS,是基于电流驱动器和在终端使用终端电阻器的电压传感器(图2)。由于接收器使用电压模式感知放大器来测量终端电阻上的电压,类似于电压模式信号,这种“电流模式”方法仍然依赖于通道上的电压摆动,限制了高通道电容的性能。

真正的电流检测放大器已在SRAM的应用中,速度是关键在读operationandvoltage swingsareproblematicduetosizing位线的司机[ 29 ] [ 31 ]–限制。类似的解决方案被应用到全球互连,并报告耗散功率少,实现更高的吞吐量比互连与最佳数量的中继器缓冲区[ 32 ] [ 36 ]。不幸的是,先前报道的电流模式接收机的带宽不足以实现我们的目标数据的一个单一的FO4门延迟的链路周期。

在本文中,我们提出了一种新的真正的电流模式串行链路,使得数据周期一个FO4门延迟,适用于恒定速率(同步)和异步操作。新的电路支持电压模式的两倍长的导线,从而大大降低了成本。这些定制电路在硬IP核的实现和交付时适用于SOC。

本文的主要贡献有三个方面。首先,我们提出了一种高速LEDR编码一个单一的FO4门延迟数据周期波流水线位串行差分链路,实现67 Gb/s模拟时使用65纳米技术的吞吐量超过7毫米。其次,我们证明了串行链路在标准位并行链路上的可扩展性优势。第三,我们提出了新的高速低功耗电流模式异步信号电路,包括65 nm的SPICE模拟。

论文的其余部分组织如下。在下一节中,我们将讨论串行和并行链路的相对性能。在第三节中,提出了单门延迟链路。第四节详细描述了异步电流模式电路及其性能。

II。并行与串行片上通信

在面积和功率方面,平行链路造成了沉重的代价。此外,并行链路性能的性能由可用时钟速率和由中继器[ 37 ]中的过程变化所引起的时钟抖动和偏移、延迟不确定性、通孔[ 38 ]和互连本身[ 38 ]、[ 39 ]、串扰噪声[ 38 ]、[ 40 ]和布局几何[ 41 ]。链路时钟频率应该足够低,以便在接收到最新数据和最早数据到达最差情况时,能够在接收机处进行可靠的数据采样。我们采用了[ 23 ]的符号,并绘制了图3中源同步通信的延迟不确定度。这将导致时钟周期的后续绑定:

(1)

其中,最大和最小的数据延迟的链路(whicharealsothe clockuncertaintyinsource同步通信),是一面时钟偏移,和,是保持接收机的时间设置触发器。

数据和时钟不确定性随着链路长度和宽度[ 28 ],[ 42 ]增长。因此,长距离链路的带宽比短程链路的带宽更为有限。为了在较长的范围内支持给定的带宽,并行链路的成本,例如,在所需的屏蔽方面,以一个超线性速率增长,长度为[ 28 ]。

图3。并行链路最小时钟周期受到时钟抖动和歪斜以及由于变化和串扰引起的平行线之间的链路长度依赖延迟差的限制。TABLE I

几种高速串行链路的数据循环

位串行通信链路的比特并行互连提供了一种替代方案,缓解地区的问题,路由和功率,因为有较少的线,少线驱动,和更少的中继器。为了支持类似于位并行链路的吞吐量,已经提出了几个异步宽带串行链路电路[ 11 ],[ 14 ] - [ 21 ],所有操作都比系统时钟快。根据最小的数据周期,表I列出了几个宽带串行链路。由于异步设计,它们对时钟抖动和歪斜不敏感。回顾(1),由于中继器和导线的更近位置,串行链路的导线偏差对过程偏差的影响比平行链路小。当没有多个比特并行进行时,串音也减少了。因此,串行链路的带宽受长度的影响小于平行链路[ 28 ]。

串行链路提出这一工作使短数据周期表一高速的设计之一是由以下novelfeatures启用:流水线转移登记,传动锁,过渡发生器,分离式架构,拆分和合并电路,编码和解码的苍蝇LEDR、线的物理设计和布局,以最小的输入电压摆幅电流快速模式接收机。下面描述了所有这些特性。

并行和串行链路[ 21 ],[ 28 ],[ 43 ]的对比分析显示了一方面链路长度和诸如动态和泄漏功率、活动区和互连区以及延迟等性能参数之间的折衷。对于固定的吞吐量,串行链路在互连区域上总是更好的,并且比并行链路更少的路由拥塞。对于超过一定长度的链接,串行链接

图4。使用串行链路的最小长度:在较长的范围内,串行链路占用的区域较少,消耗的泄漏或动态功耗比并行链路少[ 28 ]。

也优于平行林肯而言有源区,泄漏和动力[ 28 ]。相对改进随着技术扩展而增加,如图4所示,用于单个栅极延迟串行链路[ 28 ]。图中显示的链接长度,单个门延迟周期串行链路成为优越于平行连杆的泄漏和动态功率(8位字,等位和全屏蔽parallellinkwith时钟周期)。在[ 28 ]中进行了详细的比较分析。

III.单门延迟异步串行链路

该串行链路(图1)采用低延时同步器在源库[ 44 ],两相NRZ编码水平双导轨(LEDR)数据/频闪(DS)–编码[ 45 ] [ 47 ]和异步握手协议(允许非均匀延迟之间的间隔连续比特),串行器及解串器和线路驱动器和接收器。每个单词只返回一次,而不是逐位返回,从而在串行通道上以波流水线方式启用多个比特。在连接线的数据可以进一步编码的差异,受ds-de ieee1355-95标准[ 47 ]。LEDR信号优于其他串行异步协议的低功耗和高利率[ 48 ]。D和S线采用完全屏蔽的波导,使多个行进信号。在设计良好的波导上,长导线可以同时连续传输多个位。

LEDR编码在一个异或和一些传输门[ 14 ]成本极低的飞行表演。LEDR是一个系统的代码(即原始数据中包含的代码不变),因此需要在接收端没有解码器逻辑,节省功率和延迟。

|

Fig. 5. One gate-delay shift-register architecture with transmitter connections (Serializer) [15].

Fig. 6. One gate-delay shift-register architecture with receiver connections (De-Serializer) [15]. |

串行链路的数据周期不小于1 FO4门延迟[ 14 ],[ 15 ]由于数字逻辑形成的串行器及解串器电路(图。5和6,分别),包括快速的移位寄存器,可以提供和消耗一点每个FO4延迟。快速移位寄存器(SR)如图5所示。它包括独特的转换锁存器(XL)。每个XL由差分信号C/CN控制,由一个双轨道翻转controlbuffer和XLS两separatedata路径。每个XL包括一个逆变器和一个(弱)衔铁,当数据位被移位时关闭。微分控制线C / CN连接到交换机和各XL的守护者,这样,当一个开关打开时,在相同的XL的另一个是封闭的,而这种情况在邻居XLS逆转。SR包括至少两个平行管道,当偶数位被保存在底部数据路径中,奇数比特被保存在上一个数据路径中。在发射机(图5)中,数据被合并在SR输出端。输入数据在接收机(图6)前分叉到第一个XL之前的两个平行管道。c/cn控制转换,不通过控制波管道停止,在管道中移动数据。注意双数据速率操作:数据采样和移位的上升沿和下降沿的C / cn。使用多相时钟发生器[ 10 ]产生控制信号。时钟发生器是由每个新发送的单词到达时触发的。为了使高速运转,SR元件应适当大小[ 15 ]。

对于宽数据字,将SR划分为较小的子SRS并行操作,速度较慢,这是更省电的。这种划分有助于实现SR功率对其速度的线性依赖性[ 14 ]。SR被划分为每八个数据位的子SRS。

由于分区(“拆分器”架构[ 14 ]),子移位寄存器不需要在一个门延迟的最短数据周期中工作,而是在至少两倍的数据周期中工作。在发射机数据中,通过连接到XL锁存器的三状态门来加载数据(参见图5)。三态连接的电容不影响SR操作,因为SR不需要以最高的速度工作。来自子SRS的数据被合并并由合并阶段编码(图5,[ 14 ])。在接收机的大小,从线接收器出来的数据在被推到子SRS中以降低速度之前被分割级[ 14 ]分叉。合并和分割阶段使用几个放大阶段(喇叭)晶体管尺寸匹配。角应

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[21955],资料为PDF文档或Word文档,PDF文档可免费转换为Word

课题毕业论文、外文翻译、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。