英语原文共 7 页,剩余内容已隐藏,支付完成后下载完整资料

一个低压全范围可编程分频器输出频宽比为50%

关键词:工作周期,全范围,可编程分频器

摘要 :该工作提出了一个具有50%占空比输出的全范围可编程分频器。提出的可编程分频器包括一个可编程计数器(PC)和占空比改进电路(DCIC),以实现全分频范围,低占空比和接近50%占空比的输出,具有任意占空比的输入时钟。在0.18mu;mm标准CMOS制造芯片过程中,使用1.8 V电源。实验结果表明,当输入时钟频率范围为1 MHz至1 GHz,分频比范围为1至63时,所提出的可编程分频器可正常工作。对于输入时钟频率为700和1 MHz的占空比为20的输入除数,周期为20%和99.5%,输出占空比分别为50.4%和50%。所提出的可编程分频器的总功率消耗在700MHz下仅为0.62mW,并且有源芯片面积仅为0.125times;0.05mm 2。

1.介绍

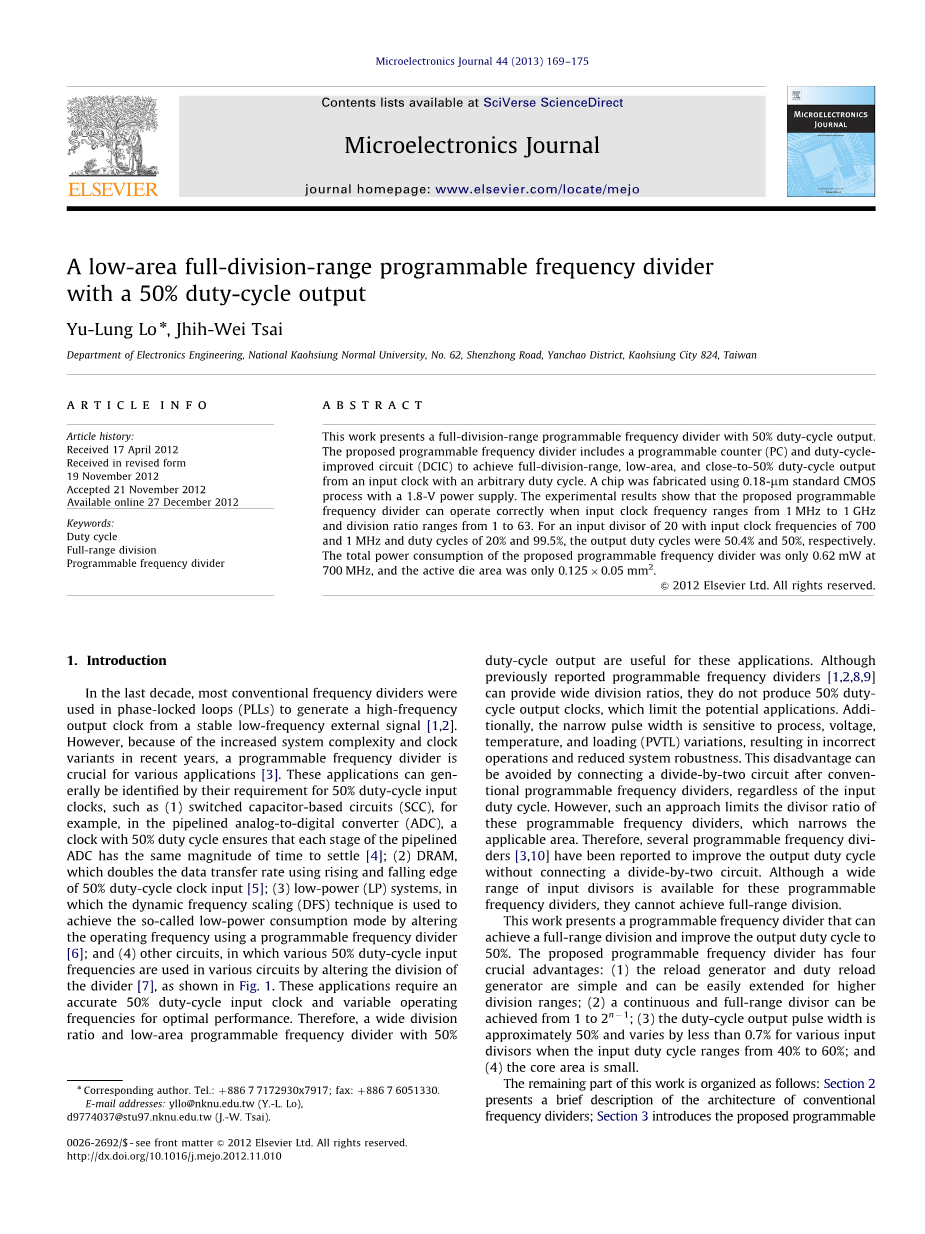

在过去的十年中,从一个稳定的低频外部信号中,大多数传统频率分隔器用锁相环来生成一个高频输出时钟[1,2]。然而,由于增加了系统的复杂性和时钟变体性。近年来,可编程分频器是各种应用程序的关键[3]。这些应用一般可以通过它们对于50%占空比输入时钟的要求来识别,例如在流水线模数转换器(ADC)中,(1)基于开关电容器的电路(SCC),时钟 50%占空比确保流水线ADC的每个级具有相同的时间稳定[4];(2)DRAM,使用上升沿和下降沿使数据传输速率加倍占空比为50%的占空比时钟输入[5]; (3)低功率(LP)系统,其中动态频率调整(DFS)技术用于通过使用可编程分频器改变工作频率来实现所谓的低功耗模式[6]; 和(4)其他电路,其中各种50%占空比输入频率通过改变分频器[7]的分频在各种电路中使用,如图1所示。使用各种频宽比50%输入频率的各电路的部门通过改变分频器[7]。为了获得最佳性能,这些应用程序需要一个精确的频宽比50%输入时钟和变量操作频率。因此,大部分比率和低压区可编程分频器以50%的频宽比输出,这些应用程序非常有用。虽然之前报道可编程频率分隔器(1、2、8、9)比率可以提供广泛的部门,它们不产生50%的频宽比输出时钟,这限制了潜在的应用。此外,窄脉冲宽度是敏感的过程,电压,温度和加载(PVTL)变化,导致不正确的操作和减少系统的稳健性。这个缺点可以避免无论输入工作周期,通过连接传统后除以2电路可编程频率分隔器。然而,这种方法限制因子比例的可编程频率分隔器,适用面积缩小。因此,几个可编程频率分隔器(3,10),来改善输出工作周期没有除以2电路连接。尽管广泛可用的输入因子是这些可编程频率分割者,但他们不能实现全过程。

这项工作提出了一种可编程分频器,可以实现全程部门,提高输出占空比为50%。拟议的可编程分频器有四个重要的优点:(1)重载生成器和责任重新加载发电机很简单,可以很容易地扩展到更高的部门范围;(2)一个连续、全程因子可以实现从1到2 n1;(3)当输入占空比范围从40%到60%,不同频宽比输出脉冲宽度大约是50%,低于0.7%的各种输入因子;(4)核心面积小。这项工作的剩余部分组织如下:第二节介绍了传统频率分隔器的架构的简要描述,第三节介绍了提出了可编程分频器设计;第四部分提供了实验结果;最后,第五节提供了一个结论。

图1 应用与改进的频宽比可编程分频器的输出

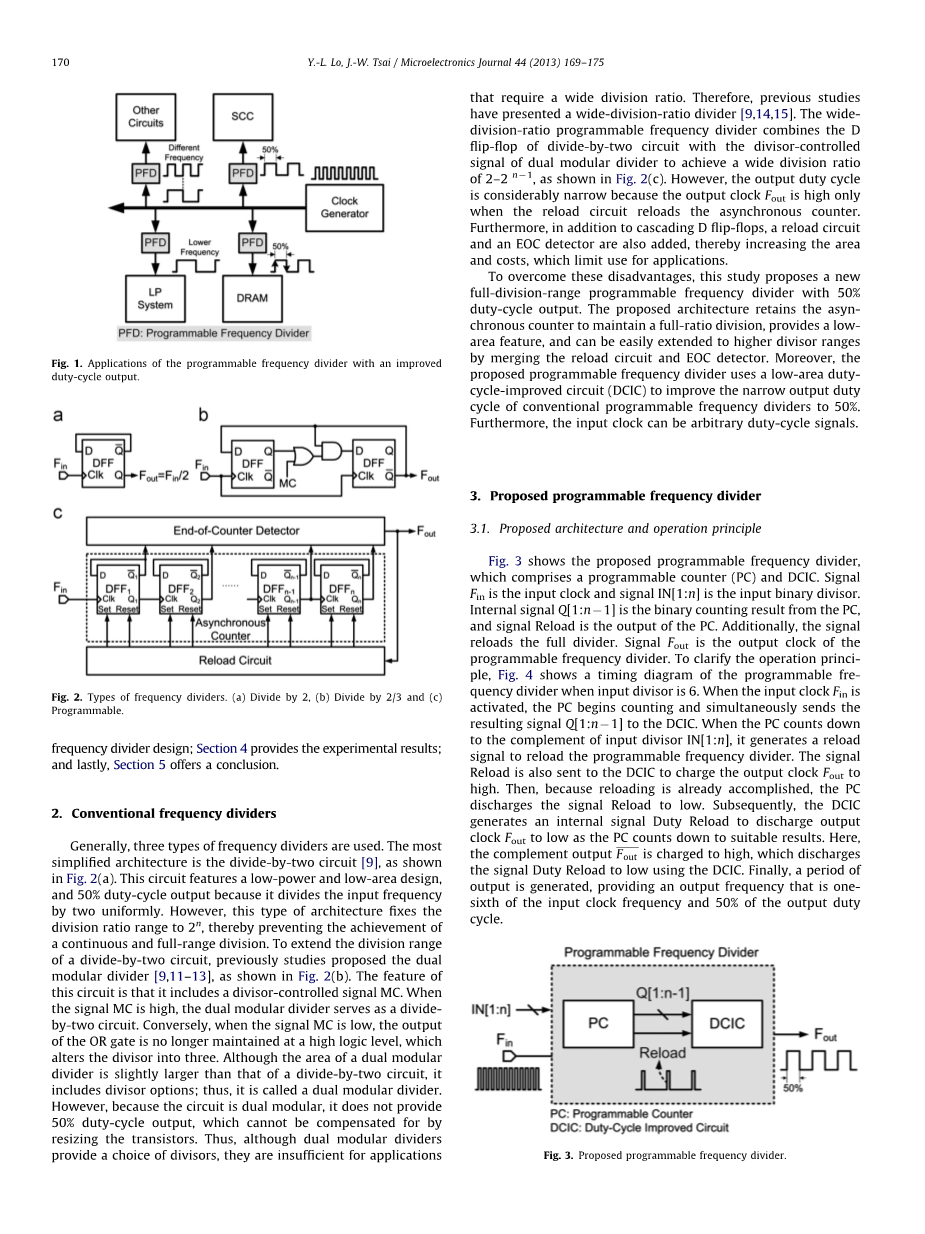

图2 类型的频率分规.(a)除以2,(b)除以2/3和(c)可编程

2.常规频率分隔器

一般来说,三种类型的使用频率分规。最简化的建筑是除以2电路[9],如图2所示。该电路具有低功耗和低压区设计,和50%的频宽比输出,因为它将由两个均匀输入频率。然而,这种类型的建筑修复的n划分比例范围内,从而防止连续的成就和进步。除以2电路扩展业务范围,先前的研究提出了双模分频器(9、11 13),如图2所示(b)。该电路的特点是,它包括一个MC 因子控制信号。当信号MC高,双模分频器划分为两个电路。相反,当信号MC低,或门的输出不再是维持在一个高电平,这改变了除数三个。尽管双模分频器的面积略大于除以2的电路,它包括除数选项;因此,它被称为双模分频器。然而,由于电路双模块化,它不提供50%的频宽比输出,不能补偿通过调整晶体管。因此,尽管双模块化分割者提供一个选择的因子,它们不足以让应用程序图需要一个广泛的部门比例。因此,先前的研究已经提出了一个广泛的分配比分配器(9,14、15)。宽分比可编程分频器结合了除以2的D触发器,电路因子控制信号的双模分频器实现广泛的部门比2 n,如图2所示(c)。然而,输出工作周期大大缩小,因为输出时钟输出端高只有当重载线路重新加载异步计数器。此外,除了层叠D人字拖,重新加载电路和一个转换端探测器也补充道,从而增加面积和成本,限制使用的应用程序。

为了克服这些缺点,本研究提出了一种新的全范围可编程分频器输出频宽比为50%,它保留异步提出的体系结构,实现计数器保持全比例部门提供低收入地区特性,可以容易地扩展到更多的除数合并范围的重新加载电路和转换端探测器。此外,提出了可编程分频器使用一个低压区责任循环改进电路(DCIC),改善狭窄输出的责任传统的循环频率可编程分规到50%。此外,可以任意频宽比输入时钟信号。

3.所示提出可编程分频器

3.1.建议的体系结构和工作原理

图3显示了该可编程分频器,它由一个可编程计数器(PC)和DCIC组成。FIN是输入时钟信号和信号在[1:n]是输入二进制除数。内部信号问(1:n1)二进制计数结果的PC,PC的输出和信号重新加载。此外,信号重新加载完整的分频器。信号输出端输出时钟的可编程分频器。图4显示了一个可编程量子的计时图,当输入因子是6,频率矫正分频器。输入时钟fin被激活时,个人电脑开始计数,同时发送的信号DCIC。当个人电脑计数输入因子的补充(1:n),它生成一个重载信号重新加载可编程分频器。信号重载也发送到DCIC收取高时钟输出端输出。然后,因为重载已经完成,PC放电信号加载到低。随后,DCIC生成内部责任重载放电输出,时钟信号输出端低PC计数到合适的结果。这里,补输出输出信号是收费高,放电信号使用DCIC责任重载低。最后,生成的输出,提供一个输出频率,第六输入时钟频率和50%的输出工作周期。

图3 可编程的分频器 图4 可编程的分频器的时序图

图5 可编程计数器

3.2.可编程计数器(PC)

为了实现与常规可编程分频器[14]相比的全分频范围特征,我们所提出的PC包括n位异步计数器和重载发生器,如图5所示。在异步计数器中,信号Q n提供给输入节点D,形成每个D触发器中的二分频级。因此,n除以二级形成n位异步,其中Q [1:n]是二进制计数结果。通常,异步计数器从2 n -1向下计数并产生结果Q [1:n]以同时控制重载发生器。重载发生器包括作为开关的2n个传输门,n个NMOS晶体管和作为伪NMOS逻辑的导通PMOS晶体管。每两个传输门和一个NMOS晶体管形成XOR门。当Q n和IN n信号在信号电平上不同时,NMOS晶体管关断,并且导通的PMOS晶体管将信号重装充电到高电平。因此,当异步计数器计数到IN [1:n]的互补时,重新加载发生器的所有NMOS晶体管被关断,并且信号重装重新加载异步计数器。 NMOS晶体管随后将信号重装放电到低以完成分频器操作。因此,信号重装的响应时间(图4)由平均充电/放电电流和PMOS晶体管的节点寄生电容。PMOS晶体管,平均充电/放电电流约为400mA,并且基于实验结果,PMOS晶体管的节点寄生电容估计42.24fF。因此,响应时间使用dt = C·dV / I c = 190ps来计算,并且结果对应于信号重装的脉冲宽度的一半。 因此,信号重装的脉冲宽度估计为380ps。

图6 占空比改进电路

所提出的PC保持全范围划分,使用低面积设计,并且可以使用简化的重载发生器容易地扩展到更高的划分范围。仅需要D触发器,两个传输门和NMOS晶体管来添加额外的位。此外,由于输入时钟F in连接到由上升沿触发的D触发器,所以输出占空比不受输入影响,而与输入占空比无关。然而,类似于常规可编程分频器,所提出的PC的重载信号提供窄输出占空比,因为只有当重载发生器重新加载异步计数器时,输出时钟才具有高逻辑电平。然而,使用占空比校正器(DCC)[5,16-19]可以避免这个缺点。这项工作提出了一个DCIC基于提出的PC的概念提高输出占空比到50%。

3.3.占空周期改善电路(DCIC)

通常,两种类型的电路用于实现常规的DCC,即非反馈型[16,17]和反馈型电路[5,18,19]。反馈型电路使用占空比检测器来识别输出占空比,并生成上升和下降信号以将其调整为50%。因此,与非反馈型电路相比,反馈型电路需要更多次锁定到稳定的环路。与反馈型电路不同,非反馈型电路使用差分种类的延迟线和时间 - 数字转换(TDC)来产生适当的上升和下降信号,实现50%的占空比输出。尽管这两种类型的电路提供不同的特征,但是常规DCC使用上升和下降信号来影响输出占空比,而不管电路的类型。因此,上升和下降信号对输出占空比至关重要,因为它们直接影响输出占空比。基于这个概念,所提出的DCIC使用二进制移位技术来改善输出占空比。

所提出的DCIC包括类似于重载发生器的占空重新加载发生器和输出控制逻辑,如图1所示。 占空比再生发生器还使用传输门和NMOS晶体管来形成nge;1个异或门。 输出控制逻辑包括D触发器,开关S1和三个NMOS晶体管。 该电路的关键特性是由二进制代码引起的二进制移位向右轻微移位与将值改变一半相同。 例如,如果输入除数是32,则32的二进制码是(100000)2,32的一半是16.16的二进制码是(010000)2,这与32的二进制码相同 向右轻微移动。

因此,占空比再加载发生器的信号IN [2:n]在异或门中右移,以将输入除数改变为其原始值的一半,如图3所示。然而,当输入除数为奇数时,二进制移位不能提供精确的变化。因此,在输出控制逻辑中包括两个NMOS晶体管(M a和M b)和开关(S 1)以评估输入除数。当PC计数到正确的结果时,占空比再加载发生器的所有NMOS晶体管(M 1 -M n)被关断,并且输出控制逻辑进入判断模式。最低有效位(LSB),IN 1,确定输入除数是奇数还是偶数;因此,当信号IN 1为高时,输入除数为奇数,使得开关S 1闭合,并且等待输入时钟F in的NMOS晶体管Ma变为低。当Fin为低时,NMOS晶体管Ma截止,并且导通的PMOS晶体管对信号职责充电重新载入高。当信号IN 1为低时,输入除数为偶数,使得开关S 1断开,并且NMOS晶体管M b使NMOS晶体管M a截止。随后,导通的PMOS晶体管将信号任务加载充电为高。评估后,输出控制逻辑使用信号重装和任务加载和D触发器将输出占空比提高到50%。当信号重装为高时,设置D触发器使输出时钟F输出充电到高,而当信号任务加载为高时,输出时钟F输出变低。同时,将F输出设置为高逻辑电平将信号任务加载放电到低,使用NMOS晶体管Mc。该技术类似于常规DCC的技术,其使用上升和下降信号来提高输出占空比。 DCIC的简单拓扑和逻辑将占空比输出脉冲宽度校正为约50%,并且还提供了可以容易地扩展到更高的除数范围的低面积设计。

3.4.功耗

为了优化所提出的架构,在设计中必须考虑功率耗散。总功耗可以分为静态和动态功耗。静态功耗由电路评估电源和各种输入除数,但没有输入时钟Fin。静态功耗包括由重新加载发生器和占空比重新加载发生器的伪NMOS架构引起的亚阈值泄漏(Ioff)和DC电流。重载发生器和占空比重载发生器中的下拉树引起静态DC消耗,并且幅度与输入除数和晶体管尺寸成比例。例如,使用(111111)2的输入除数,从信号重装和任务加载到地面看到的有效阻抗是最低,导致最大静态功耗。此外,晶体管尺寸也影响再加载发生器和负载再加载发生器的响应时间,并且必须考虑最佳性能和静态功耗。因此,所提出的分频器具有输入因数为(111111)2的最大静态功耗。相比之下,所提出的分频器具有最低静态功耗,输入除数为(000001)2。因此,静态功率仅受输入除数影响,并且与输入频率无关。

窗体顶端

动态功耗主要归因于内部节点的寄生电容器的充电/放电以及时钟转变期间的短路功率。输入时钟频率直接影响动态功耗。此外,输入除数取决于电路架构影响内部节点的切换速率。使用全定制设计方法,内部节点寄生电容被最小化,并选择最佳电路架构来实现建议的分频器。因此,随着输入时钟频率的增加和输入除数的减小,所提出的电路的有效开关频率增加,导致动态功耗的直接增加。此外,总节点寄生电容器指示必须提供的电荷数或在操作期间耗尽以对寄生的节点充电或放电,并且可以通过晶体管尺寸来优化。因此,重载和占空比再生发电机中的PMOS晶体管的尺寸是至关重要的因为它是静态功耗,动态功耗和响应时间之间的折衷,这限制了最大工作频率。

4.实验结果

提议的可编程分频器是使用标准CMOS工艺制造0.18 nm与电源电压为1.8V。图7显示了可编程分频器的模具照片,有效面积是0.125* 0.05mm2。在芯片中使用六阶段计数器是用于与以前的作品比较可编程分频器的性能。压控振荡器(VCO)也被制作来验证提出的可编程分频器。图8和图9显示输出这个提议的可编程分频器的波形当输入除数是当63和Fin分别是400兆赫和800兆赫的时候。输出

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[614130],资料为PDF文档或Word文档,PDF文档可免费转换为Word

课题毕业论文、外文翻译、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。